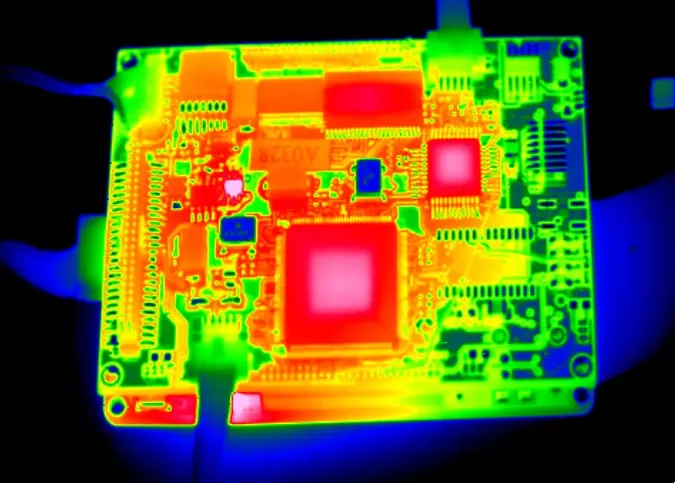

El coeficiente de dilatación térmica del material (CTE) es una propiedad física de un material. Cuando cambia la temperatura, la pieza cambia de forma y sufre tensiones. No podemos evitarlo. El núcleo de la fabricación de cualquier producto electrónico es colocar las piezas que cumplen los requisitos en una placa de circuito impreso (PCB). Las piezas se unen a la placa mediante soldadura. Para tecnología de orificios pasantes (THT), Las piezas tienen cables. Cuando la placa se dobla o se expande, el cable se dobla y absorbe parte de la tensión. El cuerpo de la pieza sufre menos tensión. Por lo tanto, cables más largos significan menos tensión en el cuerpo de la pieza. La tensión de la soldadura debida a los cambios de temperatura afecta principalmente a la junta de soldadura y a la almohadilla. Esto afecta a la fiabilidad de la soldadura.

Cuando utilizamos tecnología de montaje en superficie (SMT), podemos poner más piezas en la placa. Pero las piezas no tienen cables largos para absorber la tensión. La tensión va directamente al cuerpo de la pieza. Esto puede romper la pieza o la unión soldada si la placa y la pieza se expanden a diferentes velocidades.

Características CTE del material base FR4

Material base común reforzado con fibra de vidrio (fr4) tiene un CET diferente en el eje z (a través del grosor de la placa) y en el plano x-y (a lo largo de la placa). La placa se expandirá más en z cuando aumente la temperatura. Cuando el material está por debajo de su temperatura de transición vítrea Tg, el material está en estado vítreo y su CET es pequeño. Llamamos a este valor de CET a1. Cuando el material está por encima de Tg, el material se encuentra en un estado similar al caucho y su CET es mayor. Llamamos a este valor a2. Normalmente, a2 es aproximadamente tres veces a1.

Por ejemplo, cuando la temperatura es inferior a Tg, el CET del epoxi de fibra de vidrio en las direcciones x e y tampoco es el mismo. Difiere en aproximadamente 1 a 5 ppm/°C. En la dirección z es de aproximadamente 20 ppm/°C. Cuando un gran dispositivo de montaje superficial tiene un CET que coincide con el de la placa, esta diferencia es muy importante. Ayuda a aumentar la vida útil de la unión soldada.

Impacto de la ETC en la HTP y las microvías

El CET es un factor importante para los orificios pasantes y microvías montados en PWA. La relación de aspecto (es decir, el grosor de la placa dividido por el diámetro del orificio) de estas vías suele ser mayor que la relación de aspecto de un orificio recién taladrado en una placa desnuda. En procesos como el reflujo SMT, la extracción de piezas, el reflujo para reparación, la fabricación de placas, la fijación de bolas, la nivelación con aire caliente y la soldadura por ola, un CTE grande en dirección z provocará demasiada tensión de tracción PTH. Esto puede provocar fallos.

Por tanto, cuando elija un material para la base de la placa, primero debe pensar si su CET coincide con el CET de las piezas que se van a montar. Si no coinciden, hay que tomar medidas compensatorias.

Definición básica y significado del ETC para los PCB

Mucha gente utiliza la palabra CTE cuando habla de placas de circuito impreso. Pero, ¿cuántos saben realmente qué significa CTE y cómo empieza a afectar CTE a una placa?

CTE significa coeficiente de expansión térmica. Indica el porcentaje de cambio de tamaño cuando se calienta o enfría una placa de circuito impreso. Todos los materiales del mundo se dilatan o encogen un poco con la temperatura. Por ejemplo, una casa es ligeramente más grande en verano que en invierno.

Algunos materiales se encogen cuando se calientan, pero la mayoría se dilatan un poco cuando se calientan. La dilatación se indica en partes por millón por grado Celsius (ppm/°C). Si un PCB se expande 14 ppm/°C lateralmente, eso significa que si un PCB midiera un millón de pulgadas, crecería 14 pulgadas por cada 1°C de aumento.

Desajuste del CET entre la placa de circuito impreso y los chips de silicio

Un laminado fr4 típico tiene un CET de 14 a 17 ppm/°C. Esto parece correcto hasta que lo comparamos con un chip de silicio de gran tamaño. Muchos chips de silicio tienen un CET cercano a 6 ppm/°C. La diferencia de dilatación es lo suficientemente grande -especialmente en los grandes paquetes BGA- como para que, cuando la placa de circuito impreso y el chip se calientan, la placa de circuito impreso se dilate más que el chip. Este movimiento adicional puede arrancar las juntas de soldadura del chip.

Así que, desde el punto de vista de las placas de circuito impreso, los fabricantes suelen utilizar materiales de bajo CET. Pero, ¿cómo afecta el CET a la placa y a cómo la diseñamos y fabricamos?

Valores típicos de CET de los materiales y componentes de las placas de circuito impreso

| Material / Componente | CTE (Dirección X-Y) ppm/°C | CTE (Dirección Z) ppm/°C | Notas |

|---|---|---|---|

| Laminado FR-4 estándar | 14 - 17 | 60 - 70 (por encima de Tg puede ser >200) | Material de PCB más común |

| FR-4 de alta Tg | 12 - 16 | 50 - 60 | Mejor estabilidad térmica |

| Material de PCB de poliimida | 12 - 14 | 40 - 50 | Para aplicaciones de alta temperatura |

| Cobre | 16.5 - 17 | 16.5 - 17 | Material conductor de referencia |

| Chip de silicio | 2,6 - 3 (silicio a granel) | - | Paquete efectivo ~6 ppm/°C |

| Paquete BGA (típico) | 6 - 10 | - | Depende del tipo de sustrato |

| Envase cerámico | 6 - 8 | - | Buen ajuste del CET con el silicio |

| Aluminio | 22 - 24 | 22 - 24 | Utilizado en PCB de núcleo metálico |

| Núcleo de cobre-invar-cobre (CIC) | 8 - 10 | 8 - 10 | Núcleo metálico de bajo CET |

| Núcleo de cobre-molibdeno-cobre (CMC) | 6 - 8 | 6 - 8 | Núcleo metálico de muy bajo CET |

| Núcleo de aramida/kevlar | 7 - 8 | 7 - 8 | Material compuesto de bajo CET |

Soluciones de núcleo de PCB de bajo CET

Cuando elegimos un laminado, nos fijamos en especificaciones como Tg, constante dieléctrica Dk y factor de disipación Df, entre otras. Todas ellas son importantes y se afectan mutuamente. Si elegimos un laminado para reducir el CET, veremos que todos los tipos de fr4 tienen valores de CET similares. La mayoría siguen siendo altos (alrededor de 14 ppm/°C). Esto significa que para paquetes de silicio muy grandes necesitamos otro enfoque para controlar el CTE. Una forma es añadir un núcleo de metal, Kevlar o aramida.

Estos núcleos de bajo CET se utilizan a menudo bajo capas exteriores fr4 para fabricar placas de bajo CET. Los núcleos metálicos pueden ser de cobre-invar-cobre (CIC) o de cobre-molibdeno-cobre (CMC). Suelen tener un grosor de unos 6 mil. El cobre de la superficie exterior del núcleo metálico nos permite laminar preimpregnados y núcleos fr4 normales sobre el metal.

Dos núcleos metálicos muy utilizados son CIC y CMC. Sus valores de CET del núcleo son de aproximadamente 8 ppm/°C y 6 ppm/°C, respectivamente. Cuando se anclan capas exteriores fr4 a un núcleo metálico, el CET total de la placa pasa a ser de unas 12 ppm/°C para CIC y de unas 9 ppm/°C para CMC.

También podemos utilizar un Kevlar Thermount o un laminado de aramida como núcleo. Su CTE de núcleo bajo es de aproximadamente 7 a 8 ppm/°C. Con capas exteriores de fr4 estándar, el CET de toda la placa pasa a ser de unas 12 ppm/°C. En la producción multicapa, un núcleo de bajo CET sustituye a un núcleo fr4 típico. Es interesante que la fibra Kevlar tenga una expansión térmica negativa. Cuando unimos las fibras con epoxi, el resultado es un pequeño CET positivo.

Coste, proceso y ventajas adicionales de los núcleos de bajo CET

Con un laminado de bajo CET, la opción más cara suele ser el núcleo metálico. Los laminados de kevlar y aramida cuestan menos. En el pasado, el Kevlar Thermount de Arlon era difícil de conseguir, pero ahora la nueva producción aumenta la oferta. Todos los núcleos de bajo CET son más difíciles de perforar y procesar. Pero son la única forma de satisfacer las necesidades de 6-9 ppm/°C de los paquetes de silicio muy grandes.

Además de controlar el CTE, las placas de circuito impreso con núcleo metálico también pueden mejorar la transferencia de calor de alta potencia. Recuerde que el metal se expande más que el fr4 cuando se calienta. Un núcleo metálico proporciona un mayor control de la expansión de la placa que el Kevlar. Un núcleo metálico puede cambiar la expansión de toda la placa más que el Kevlar.

Medidas prácticas para reducir el riesgo de desajuste del CTE

En la práctica, para reducir el riesgo de desajuste del CTE se pueden hacer estas cosas básicas:

Intente hacer coincidir el CTE de la placa con el CTE del paquete grande siempre que pueda.

Utilice núcleos de bajo CET como CIC, CMC, Kevlar o aramida para paquetes grandes.

Vigile la Tg y utilice materiales con una Tg superior a su temperatura de proceso más alta.

Para las piezas SMT, diseñe almohadillas y patrones de aterrizaje para reducir la tensión en las juntas de soldadura.

En la fabricación, controlar los picos de temperatura de reflujo y las velocidades de enfriamiento.

Para las piezas con orificios pasantes, utilice cables que puedan flexionarse para absorber la tensión.

Sepa que los núcleos de bajo CET cuestan más y necesitan herramientas y procesos de perforación diferentes.

Resumen de la importancia de la CTE

El CTE es un número sencillo, pero afecta a muchas partes de un proyecto de PCB. Si no se piensa en ello desde el principio, se pueden producir fallos en las juntas de soldadura, grietas en las piezas y una baja fiabilidad. Si planifica el CTE desde el principio, obtendrá una mayor vida útil de su placa y sus piezas.