材料の熱膨張係数(CTE)は、材料の物理的特性のひとつである。温度が変化すると、部品は形状を変え、応力が発生する。それを止めることはできない。あらゆる電子製品の製造の核心は、プリント基板(PCB)の上に要件を満たす部品を配置することです。私たちは、はんだ付けによって部品を基板に接合します。そのために スルーホール技術(THT), 部品にはリード線がある。基板が曲げられたり膨張したりすると、リードが曲がって応力を吸収する。そうすると部品本体にかかるストレスは少なくなる。つまり、リードが長ければ長いほど、部品本体にかかる応力は小さくなります。温度変化によるはんだ応力は、主にはんだ接合部とパッドに影響します。それがはんだの信頼性に影響するのです。.

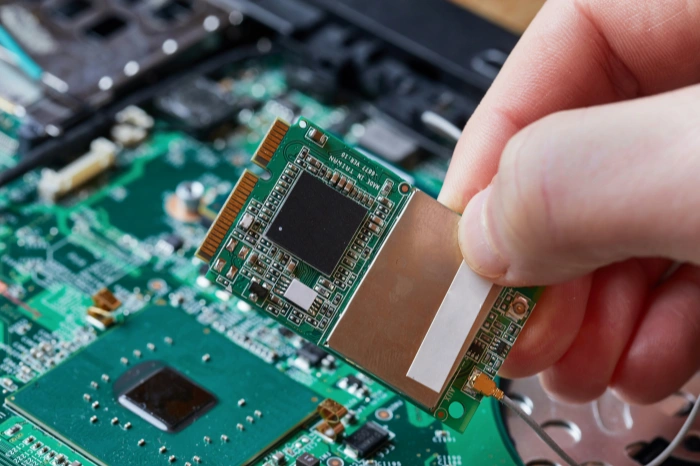

を使用する場合 表面実装技術(SMT), そのため、より多くのパーツを基板上に配置することができる。しかし、部品にはストレスを吸収するための長いリード線がない。ストレスは部品本体に直接伝わります。基板と部品の膨張率が異なれば、部品やはんだ接合部が壊れる可能性がある。.

FR4母材のCTE特性

一般的なガラス繊維強化基材(fr4) は、z軸方向(基板の厚みを通る方向)とx-y平面方向(基板に沿った方向)でCTEが異なります。温度が上昇すると、基板はz方向に大きく膨張する。材料がガラス転移温度Tg以下の場合、材料はガラス状態にあり、そのCTEは小さい。このCTE値をa1と呼ぶ。材料がTg以上の場合、材料はゴムのような状態にあり、そのCTEは大きくなります。このCTE値をa2と呼ぶ。通常、a2はa1の約3倍です。.

例えば、温度がTg以下の場合、ガラス繊維エポキシのX方向とY方向のCTEは同じではありません。約1~5ppm/℃の差がある。z方向では約20ppm/℃の差がある。大型の表面実装デバイスが基板と一致するCTEを持つ場合、この差は非常に重要です。はんだ接合部の寿命を延ばすのに役立ちます。.

PTHとマイクロビアに対するCTEの影響

CTEは、PWAに実装されるスルーホールやマイクロビアにとって重要な要素である。これらのビアのアスペクト比(基板の厚さを穴の直径で割った値)は、通常、ベア基板にドリルで穴を開けただけの状態のアスペクト比よりも大きくなります。SMTリフロー、部品除去、リペア用リフロー、基板製造、ボール取り付け、熱風レベリング、ウェーブはんだなどの工程では、Z方向のCTEが大きいとPTHの引張応力が大きくなりすぎます。これは故障の原因となります。.

そのため、基板ベース材を選ぶ際には、まずそのCTEが実装する部品のCTEと合っているかどうかを考える必要がある。一致しない場合は、補償措置を講じる必要がある。.

PCBのCTEに関する基本的な定義と意義

PCBについて語るとき、多くの人がCTEという言葉を使う。しかし、CTEが何を意味するのか、またCTEが基板にどのような影響を与え始めるのかを本当に知っている人はどれほどいるのだろうか。

CTEは熱膨張係数の略。プリント基板を加熱または冷却したときのサイズの変化率を示します。世の中のあらゆる材料は、温度によって少しずつ膨張したり収縮したりします。例えば、家は冬よりも夏の方がわずかに大きくなります。.

加熱すると収縮する材料もあるが、ほとんどの材料は加熱すると少し膨張する。膨張は100万分の1℃(ppm/℃)で示される。PCBが横方向に14ppm/℃膨張する場合、PCBが100万インチの長さであれば、1℃上昇するごとに14インチ伸びることを意味します。.

PCBとシリコンチップ間のCTEミスマッチ

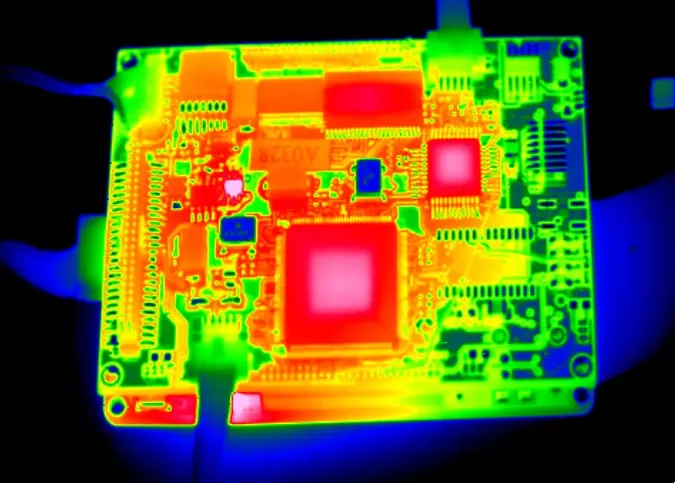

典型的なfr4ラミネートのCTEは14~17ppm/℃である。これは、大型シリコンチップと比較するまでは大丈夫に見える。多くのシリコンチップのCTEは6ppm/°Cに近い。この膨張の差は十分に大きく、特に大型のBGAパッケージでは、PCBとチップが熱を持つと、PCBがチップよりも大きく膨張します。この余分な動きが、はんだ接合部をチップから引き剥がす可能性があります。.

そのため、PCBの観点からは、メーカーは低CTE材料を使用することが多い。しかし、CTEは基板にどのような影響を与えるのでしょうか?

PCB材料と部品の代表的なCTE値

| 素材/部品 | CTE(X-Y方向) ppm/°C | CTE(Z方向) ppm/°C | 備考 |

|---|---|---|---|

| 標準FR-4ラミネート | 14 - 17 | 60~70(Tg以上は200を超えることもある) | 最も一般的なPCB材料 |

| 高Tg FR-4 | 12 - 16 | 50 - 60 | より優れた熱安定性 |

| ポリイミドPCB材料 | 12 - 14 | 40 - 50 | 高温用途に使用 |

| 銅 | 16.5 - 17 | 16.5 - 17 | 参考導体材料 |

| シリコンチップ | 2.6 - 3(バルクシリコン) | - | パッケージ実効 ~6 ppm/°C |

| BGAパッケージ(代表値) | 6 - 10 | - | 基板の種類による |

| セラミックパッケージ | 6 - 8 | - | シリコンとの良好なCTEマッチング |

| アルミニウム | 22 - 24 | 22 - 24 | メタルコアPCBに使用 |

| 銅-インバー銅(CIC)コア | 8 - 10 | 8 - 10 | 低熱膨張率メタルコア |

| 銅-モリブデン-銅(CMC)コア | 6 - 8 | 6 - 8 | 超低CTEメタルコア |

| アラミド/ケブラーコア | 7 - 8 | 7 - 8 | 低CTE複合材料 |

低CTE PCBコアソリューション

ラミネートを選ぶとき、私たちはTg、誘電率Dk、誘電正接Dfなどのスペックに注目します。これらはすべて重要で、互いに影響し合う。CTEを低くするためにラミネートを選ぶと、どのfr4タイプも似たようなCTE値を持っていることがわかります。大半はまだ高い(約14ppm/℃)。つまり、非常に大きなシリコン・パッケージには、CTEを制御する別のアプローチが必要なのだ。一つの方法は、金属、ケブラー、またはアラミド製のコアを追加することです。.

これらの低CTEコアは、低CTEボードを作るためにfr4外層の下に使われることが多い。金属コアは、銅-インバー銅(CIC)または銅-モリブデン-銅(CMC)である。厚さは通常約6ミルです。金属コアの外面に銅を使用することで、通常のfr4プリプレグやコアを金属の上にラミネートすることができます。.

広く使用されている2つの金属コアはCICとCMCである。これらのコアのCTE値はそれぞれ約8ppm/℃と約6ppm/℃である。fr4外層を金属コアに固定すると、基板全体のCTEはCICで約12ppm/℃、CMCで約9ppm/℃になる。.

ケブラー・サーモウントやアラミド・ラミネートをコアとして使用することもできます。これらの低コアCTEは約7~8ppm/℃です。標準的なfr4外層を使用すると、基板全体のCTEは約12ppm/℃になります。多層製造では、低CTEコアが一般的なfr4コアに取って代わる。興味深いのは、ケブラー繊維が実は負の熱膨張率を持っていることです。繊維をエポキシで結合すると、結果としてCTEがわずかにプラスになります。.

低CTEコアのコスト、プロセス、その他の利点

低CTEラミネートを使用する場合、最も高価なオプションは通常メタルコアである。ケブラーやアラミドのラミネートはコストが低い。以前はアーロンケブラーサーマウントは入手が困難でしたが、現在は新しい生産により供給量が増えています。低CTEコアはいずれも穴あけや加工が難しい。しかし、超大型シリコンパッケージの6~9ppm/℃のニーズを満たす唯一の方法です。.

CTEを制御するだけでなく、メタルコアPCBはハイパワーの熱伝達を改善することができる。金属は加熱されるとfr4よりも膨張することを覚えておいてください。メタルコアは、ケブラーよりも基板の膨張を制御できます。メタルコアは、ケブラーよりも基板全体の膨張を変えることができます。.

CTEミスマッチリスク低減のための実践的対策

実際には、CTEミスマッチのリスクを減らすために、以下のような基本的なことができる:

できる限り、ボードのCTEと大型パッケージのCTEを一致させるようにしてください。.

大型パッケージには、CIC、CMC、ケブラー、アラミドなどの低CTEコアを使用する。.

Tgに注意し、最高プロセス温度以上のTgを持つ材料を使用する。.

SMT部品では、はんだ接合部のストレスを軽減するためにパッドとランドパターンを設計します。.

製造では、リフローのピーク温度と冷却速度を制御する。.

スルーホール部品には、応力を受け止めるために屈曲可能なリードを使用する。.

低CTEコアはより高価であり、異なる掘削工具と工程が必要である。.

CTEの重要性のまとめ

CTEは単純な数値ですが、PCBプロジェクトの多くの部分に影響します。早めに考えないと、はんだ接合部の不具合や部品のひび割れ、信頼性の低下などが発生します。最初からCTEを考慮した計画を立てれば、基板や部品の寿命を延ばすことができます。.