Bảng mạch in HDI là gì?

Bảng mạch HDI là bảng mạch in có mật độ kết nối cao. Loại bảng mạch này sử dụng các lỗ vias mù và lỗ vias chôn ngầm. Các bảng mạch này có mật độ đường dẫn cao. Chúng bao gồm các đường dẫn trên lớp trong và lớp ngoài. Ngoài ra, chúng còn sử dụng các lỗ khoan và lỗ mạ để kết nối các đường dẫn giữa các lớp. Khi các sản phẩm điện tử ngày càng nhỏ gọn và chính xác hơn, các nhà sản xuất yêu cầu các bảng mạch in (PCB) có mật độ cao hơn. Cách tốt nhất để tăng mật độ PCB là giảm số lượng lỗ xuyên qua và thêm các lỗ vias mù và lỗ vias chôn được bố trí hợp lý. Nhu cầu này đã dẫn đến sự ra đời của bảng mạch HDI.

Định nghĩa IPC

IPC-2226 đưa ra một quy tắc rõ ràng đối với các lỗ vias bị che khuất và chôn ngầm:

-

Đường kính của lỗ dẫn hoặc lỗ dẫn chôn ngầm ≤ 0,15 mm (0,00591 inch).

-

Đường kính vòng tròn ≤ 0,35 mm (0,0138 inch).

-

Các lỗ vias này có thể được tạo ra bằng cách khoan laser hoặc khoan cơ học, hoặc bằng phương pháp ăn mòn khô/ướt, hoặc bằng phương pháp chuyển mẫu. Sau đó, một lớp mạ dẫn điện sẽ phủ lên lỗ.

Lưu ý: Nếu đường kính lỗ lớn hơn 0,15 mm (0,00591 inch), hãy coi đó là lỗ xuyên theo tiêu chuẩn tương tự.

Các kích thước lỗ khoan thông dụng cho HDI

Các kích thước đường dẫn phổ biến cho HDI là 3–5 mil. Các nhà thiết kế thường sử dụng 4 mil làm giá trị trung bình cho quá trình thiết kế và sản xuất.

Các tiêu chuẩn IPC phổ biến được sử dụng cho HDI

Các tiêu chuẩn IPC tiêu biểu cho công việc HDI bao gồm:

-

IPC/JPCA-2315 — Hướng dẫn thiết kế cấu trúc kết nối mật độ cao và lỗ vi mạch.

-

IPC-2226 — Tiêu chuẩn thiết kế cho bảng mạch in kết nối mật độ cao (HDI).

-

IPC/JPCA-4104 — Tiêu chuẩn về việc xác nhận và đánh giá hiệu suất của vật liệu điện môi cho các cấu trúc HDI.

-

IPC-6016 — Tiêu chuẩn về chứng nhận và hiệu suất cho các cấu trúc HDI.

Định tuyến HDI: những thách thức và lời khuyên

Định tuyến HDI là gì

Định tuyến HDI là việc áp dụng các ý tưởng thiết kế và phương pháp sản xuất tiên tiến nhất để tạo ra bố cục mạch dày đặc hơn mà không làm thay đổi chức năng của mạch. Nói tóm lại, HDI sử dụng nhiều lớp định tuyến hơn, đường dẫn nhỏ hơn, lỗ vias nhỏ hơn, điểm tiếp xúc nhỏ hơn và lõi mỏng hơn. Điều này cho phép tích hợp các mạch phức tạp và thường là mạch tốc độ cao vào những không gian mà trước đây không thể thực hiện được.

Khi các phương pháp sản xuất ngày càng được cải tiến, việc bố trí mạch HDI đã xuất hiện trong nhiều thiết kế. Bạn có thể tìm thấy HDI trong bo mạch chủ, card đồ họa, điện thoại di động và các thiết bị khác có không gian hạn chế. Nếu thực hiện bố trí mạch HDI đúng cách, bạn có thể thu nhỏ kích thước bo mạch và đồng thời giảm thiểu các vấn đề nhiễu điện từ (EMI) trên PCB. Giảm chi phí là mục tiêu quan trọng của nhiều doanh nghiệp. Việc bố trí mạch HDI giúp đạt được mục tiêu đó.

Định tuyến HDI và lỗ vi mạch

Quá trình bố trí mạch HDI phức tạp hơn so với bố trí mạch đa lớp thông thường. Có thể bạn đã biết cách thiết kế các bảng mạch in (PCB) 8 lớp hoặc 16 lớp. Tuy nhiên, công nghệ HDI mang đến những khái niệm mới mà bạn cần phải nắm vững.

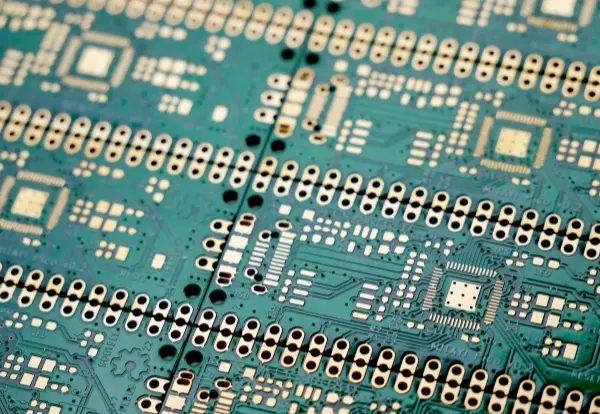

Trong một bảng mạch in (PCB) thông thường, chúng ta xem toàn bộ bảng mạch như một đơn vị duy nhất gồm nhiều lớp. Trong công nghệ HDI, các nhà thiết kế phải xem xét nhiều lớp siêu mỏng được xếp chồng lên nhau để tạo thành một bảng mạch. Yếu tố chính quyết định việc bố trí đường dẫn trong HDI chính là công nghệ lỗ thông (via). Các lỗ thông không còn chỉ là những lỗ được mạ kim loại và khoan xuyên qua cấu trúc xếp chồng đã hoàn thiện. Các lỗ xuyên truyền thống làm giảm diện tích có sẵn cho việc bố trí đường dẫn trên mỗi lớp.

Các lỗ dẫn truyền truyền thống không phù hợp với HDI

Trong quy trình định tuyến HDI, các lỗ vias siêu nhỏ đóng vai trò then chốt. Chúng cho phép nhiều lớp dày đặc kết nối với nhau. Cụ thể, các lỗ vias siêu nhỏ trông giống như các lỗ vias mù hoặc chôn ngầm nhưng được thực hiện theo phương pháp khác. Các lỗ vias truyền thống được khoan sau khi các lớp đã được xếp chồng lên nhau. Trong khi đó, các lỗ vias siêu nhỏ được khoan bằng laser trực tiếp trên các lớp trước khi xếp chồng. Các lỗ vias siêu nhỏ được khoan bằng laser cho phép kích thước lỗ và kích thước điểm tiếp xúc nhỏ nhất giữa các lớp. Điều này giúp BGA các bố cục phân nhánh trong đó các chân cắm được bố trí theo dạng lưới.

Các chiến lược định tuyến HDI

Với công nghệ microvia, các nhà thiết kế PCB có thể bố trí mạng mạch phức tạp trên nhiều lớp. Phương pháp này đôi khi được gọi là “HDI đa lớp” hoặc “kết nối từng lớp”. Do microvia giúp tiết kiệm không gian, cả hai lớp ngoài đều có thể chứa các linh kiện dày đặc trong khi phần lớn mạng mạch được bố trí trên các lớp bên trong.

Các mặt phẳng nối đất có trở kháng thấp là rất quan trọng

Khi mật độ linh kiện và đường mạch trên bảng mạch nhiều lớp tăng lên, nguy cơ nhiễu điện từ (EMI) và hiện tượng ghép từ sẽ gia tăng. Trong thiết kế HDI, bạn phải đảm bảo cấu trúc lớp xếp chồng phù hợp. Cần bố trí đủ các lớp mặt đất để tạo ra các đường dẫn trở về có trở kháng thấp.

Đặt các lớp định tuyến bên trong giữa các lớp nối đất hoặc lớp nguồn để giảm hiện tượng ghép chéo và nhiễu chéo. Giữ cho các đường dẫn tín hiệu tốc độ cao ngắn và các đường dẫn trở về cũng phải ngắn. Thiết kế các lỗ vi mạch sao cho chúng giới hạn các đường dẫn tín hiệu trong một khu vực nhỏ. Điều này giúp giảm nguy cơ nhiễu điện từ (EMI).

Vì lý do an toàn, hãy sử dụng các công cụ mô phỏng phù hợp để mô phỏng bảng mạch in HDI trước khi sản xuất.

Những lợi ích chính của bảng mạch in HDI

Nhiều người mong muốn giảm kích thước sản phẩm. Một trong những cách hiệu quả nhất là sử dụng bảng mạch in HDI. Khi bạn cần giảm trọng lượng và kích thước nhưng vẫn đảm bảo chức năng và độ tin cậy, HDI là một giải pháp phù hợp.

Những lợi ích chính:

-

HDI cho phép sử dụng các lỗ pad-in-pad và lỗ mù. Điều này giúp các linh kiện được bố trí gần nhau hơn và giảm chiều dài đường dẫn. Đường dẫn ngắn hơn thường mang lại tín hiệu nhanh hơn và đáng tin cậy hơn.

-

Các bo mạch này mang lại hiệu suất tốt với mức giá hợp lý. HDI là lựa chọn phù hợp về mặt chi phí cho những ai cần các thiết bị điện tử đáng tin cậy và bền bỉ.

-

Để xác định xem HDI có phù hợp với dự án của bạn hay không, hãy tìm hiểu thêm về công nghệ này và cách sử dụng nó. Nắm rõ sự khác biệt giữa PCB thông thường và PCB HDI.

Hiện nay, PCB HDI được ứng dụng ở đâu

Nhờ những ưu điểm của mình, bảng mạch in HDI được ứng dụng rộng rãi trong nhiều lĩnh vực.

-

Thiết bị y tế — Nhiều dụng cụ y tế phải có kích thước nhỏ gọn. Thiết bị phòng thí nghiệm và các thiết bị cấy ghép thường cần các bảng mạch siêu nhỏ. Công nghệ HDI phát huy tác dụng trong những trường hợp này. Máy tạo nhịp tim là một ví dụ điển hình. Nhiều thiết bị theo dõi và thăm dò, như ống nội soi, cũng sử dụng công nghệ HDI. Trong những trường hợp này, kích thước càng nhỏ thì càng tốt.

-

Ô tô — Xe ô tô tận dụng không gian một cách hiệu quả. Một số thiết bị điện tử trên xe đang ngày càng nhỏ gọn hơn. Công nghệ HDI giúp giảm kích thước mà vẫn đảm bảo chức năng.

-

Thiết bị di động — Máy tính bảng và điện thoại sử dụng HDI. Đó là lý do tại sao các thiết bị này ngày càng mỏng hơn theo thời gian.

-

Hàng không vũ trụ và quốc phòng — Các lĩnh vực này sử dụng HDI nhờ tính ổn định và kích thước nhỏ gọn của nó. HDI ngày càng được ứng dụng rộng rãi hơn khi các thiết kế mới đòi hỏi các bo mạch nhỏ gọn và ổn định.

Trong tương lai, nhiều lĩnh vực khác sẽ áp dụng Chỉ số Phát triển Con người (HDI) nhiều hơn.

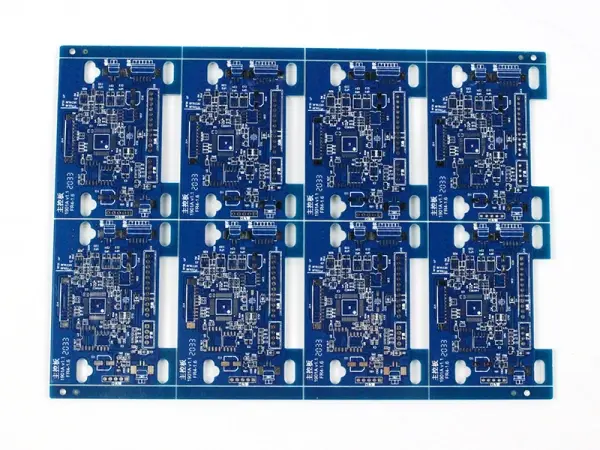

Điều gì làm nên một bảng mạch in HDI?

Một bảng mạch in HDI sử dụng phương pháp mạ lỗ mù và sau đó là bước ép lớp thứ hai. Các bảng mạch này có thể thuộc cấp độ 1, cấp độ 2, cấp độ 3 hoặc cao hơn. Các nhà sản xuất thường chế tạo bảng mạch HDI theo từng bước ép lớp. Số bước ép lớp càng nhiều thì cấp độ kỹ thuật càng cao.

-

Các bảng mạch HDI cơ bản thường chỉ trải qua một công đoạn ép lớp.

-

Chỉ số phát triển con người (HDI) ở mức cao hơn sử dụng hai hoặc nhiều bước ép lớp.

-

Các mạch in có chỉ số phát triển con người (HDI) cấp cao có thể sử dụng các lỗ vias xếp chồng, lỗ vias mạ và lấp đầy, khoan trực tiếp bằng laser và các phương pháp tiên tiến khác.

Bây giờ chúng ta sẽ giải thích về các cấu trúc lớp phổ biến và cách các nhà phát triển xây dựng chúng.

Bảng mạch HDI đơn lớp đơn giản (ví dụ)

Một bảng mạch HDI đơn lớp đơn giản có thể là bảng mạch 6 lớp với cấu trúc xếp chồng 1+4+1. Bảng mạch này rất đơn giản. Phần bảng mạch đa lớp bên trong không có lỗ vias chôn ngầm. Chỉ cần một lần ép lớp là hoàn thành bảng mạch. Quy trình sản xuất tương tự như các bảng mạch đa lớp đơn lớp thông thường. Tuy nhiên, sau khi ép lớp, bạn vẫn cần tiến hành khoan laser cho các lỗ vias mù và các bước khác.

HDI một lớp thông thường (trường hợp phổ biến)

Một bảng mạch HDI một lớp thông thường có cấu trúc (1 + N + 1), trong đó N ≥ 2 và N là số chẵn. Ví dụ, một HDI 6 lớp đơn lớp sử dụng cấu trúc 1+4+1. Cấu trúc này là thiết kế chủ đạo cho HDI đơn lớp. Lớp đa lớp bên trong thường có các lỗ vias chôn ngầm, đòi hỏi một bước ép lớp thứ hai để hoàn thiện. Loại HDI đơn lớp này thường có các lỗ vias mù và lỗ vias chôn ngầm. Nếu các nhà thiết kế có thể chuyển đổi loại này thành dạng đơn lớp đơn giản như trên, cả người mua và nhà cung cấp đều được lợi.

HDI hai lớp thông thường (trường hợp phổ biến)

Một bảng mạch HDI hai lớp phổ biến có thể là bảng mạch 8 lớp với cấu trúc xếp chồng 1+1+4+1+1. Cấu trúc xếp chồng này là (1+1+N+1+1) với N ≥ 2 và là số chẵn. Đây là thiết kế hai lớp chủ đạo trong ngành công nghiệp PCB. Lớp đa lớp bên trong có các lỗ vias chôn ngầm cần ba bước ép lớp. Loại này thường không có cấu trúc xếp chồng lỗ vias lệch pha. Nếu bạn có thể chuyển các lỗ vias chôn ngầm từ các lớp 3–6 sang các lớp 2–7, bạn có thể giảm bớt một bước ép lớp và tiết kiệm chi phí.

Một loại HDI hai lớp phổ biến khác

Loại này cũng sử dụng cấu trúc (1+1+N+1+1). Mặc dù đây là cấu trúc hai lớp, nhưng lỗ via chôn ngầm lại nằm ở vị trí khác — giữa lớp 2 và lớp 7. Sự thay đổi này có thể giúp giảm số bước ép lớp từ ba xuống còn hai. Tuy nhiên, thiết kế này có một điểm khó khăn: nó có thể tạo ra các lỗ via mù từ các lớp 1–3. Bạn phải chia chúng thành hai bộ (1–2 và 2–3) và tạo các lỗ dẫn nội bộ 2–3 bị che khuất bằng cách lấp đầy lỗ dẫn. Việc lấp đầy lỗ dẫn làm tăng chi phí và độ khó. Vì vậy, trong quá trình thiết kế, hãy cố gắng tránh các lỗ dẫn xếp chồng lên nhau và thay đổi các lỗ dẫn bị che khuất 1–3 thành các lỗ dẫn bị che khuất và lỗ dẫn chôn lấp 1–2 và 2–3 xen kẽ.

Loại HDI hai lớp hiếm gặp có lỗ thông mù xuyên lớp

Một loại bảng mạch HDI 6 lớp hai lớp laminate không phổ biến sử dụng cấu trúc 1+1+2+1+1. Thiết kế này vẫn áp dụng nguyên lý (1+1+N+1+1) với N ≥ 2 và là số chẵn. Thiết kế này có các lỗ mù xuyên lớp. Độ sâu của lỗ mù tăng lên — lỗ mù có độ sâu 1–3 gấp đôi độ sâu của lỗ mù thông thường 1–2. Khách hàng chọn thiết kế này có nhu cầu cụ thể và không muốn lỗ mù được chia thành các lỗ xếp chồng lên nhau. Các lỗ mù xuyên lớp này rất khó khoan bằng laser. Việc lắng đọng đồng và mạ trên các lỗ mù sâu như vậy cũng rất khó khăn.

Thiết kế lỗ thông qua xếp chồng trong bảng mạch HDI hai lớp

Có một loại bảng mạch trong đó các lỗ vias chôn ngầm ở các lớp 2–7 cần có các lỗ vias mù xếp chồng phía trên. Đây vẫn là cấu trúc (1+1+N+1+1). Một số bảng mạch HDI hai lớp sử dụng phương pháp này. Phần nhiều lớp bên trong có các lỗ vias chôn ngầm và cần hai bước ép lớp. Điểm mấu chốt là thiết kế lỗ vias xếp chồng làm tăng độ phức tạp. Tuy nhiên, việc đặt các lỗ vias chôn ngầm ở các lớp 2–7 giúp giảm bớt một bước ép lớp và tiết kiệm chi phí.

Thiết kế lỗ thông qua mù xuyên lớp trong bảng mạch HDI hai lớp

Một thiết kế nhiều lớp kép khác (1+1+N+1+1) bao gồm các lỗ thông mù xuyên lớp. Thiết kế này khó sản xuất hơn và một số nhà sản xuất HDI chưa có đủ kỹ năng để thực hiện. Phần nhiều lớp bên trong có các lỗ thông chôn ngầm ở các lớp 3–6 và cần ba bước ép lớp. Vấn đề chính là thiết kế lỗ dẫn mù xuyên lớp. Nếu bạn có thể chia lỗ dẫn xuyên lớp 1–3 thành các lỗ dẫn mù 1–2 và 2–3, chi phí sẽ giảm và quy trình trở nên đơn giản hơn. Lưu ý: sự chia tách này khác với sự chia tách lỗ dẫn xếp chồng đã giải thích trước đó. Sự chia tách này sử dụng các lỗ dẫn mù so le thay vì các lỗ dẫn mù xếp chồng.

Các mức độ của Chỉ số Phát triển Con người (HDI)

-

Chỉ số Phát triển Con người (HDI) cấp độ 1 (cấp 1) khá đơn giản. Quá trình thực hiện và việc kiểm soát cũng dễ dàng hơn.

-

Chỉ số Phát triển Con người (HDI) cấp hai phức tạp hơn trong lĩnh vực sản xuất và chế tạo.

-

Các cấp độ từ cấp 3 trở lên tuân theo các quy tắc của cấp độ 2 nhưng phức tạp hơn.

Sự khác biệt giữa HDI và PCB thông thường

Bảng mạch HDI thường được sản xuất bằng kỹ thuật ép lớp sử dụng vật liệu lõi mỏng. Số lớp ép càng nhiều thì mức độ phức tạp của quy trình càng cao. Hầu hết các bảng mạch HDI chỉ sử dụng một lớp ép. Các bảng mạch HDI cao cấp sử dụng hai hoặc nhiều kỹ thuật ép lớp và kết hợp các phương pháp tiên tiến như lỗ vias xếp chồng, lỗ vias mạ lấp đầy và khoan trực tiếp bằng laser.

Khi mật độ tương đối của một bảng mạch in (PCB) cao hơn so với bảng mạch tám lớp, việc sản xuất bằng công nghệ HDI thường có chi phí thấp hơn so với quy trình ép và dán lớp truyền thống phức tạp. Các bảng mạch HDI thường có độ bền cơ học cao hơn và độ chính xác tín hiệu tốt hơn so với các bảng mạch in truyền thống.

Những cải tiến khác của HDI so với PCB thông thường:

-

Hiệu suất tốt hơn đối với tín hiệu vi sóng và tần số vô tuyến.

-

Khả năng chống nhiễu sóng vô tuyến và phóng điện tĩnh tốt hơn.

-

Khả năng dẫn nhiệt tốt hơn.

Công nghệ tích hợp mật độ cao (HDI) giúp các sản phẩm cuối cùng trở nên nhỏ gọn hơn và đồng nhất hơn về chức năng cũng như hiệu suất.

Một số lời khuyên đơn giản dành cho các nhà thiết kế và người mua

-

Hãy sử dụng HDI khi bạn cần kích thước nhỏ gọn hơn và hiệu suất cao hơn.

-

Hãy liên hệ với nhà cung cấp PCB của bạn từ sớm. PCB HDI cần được kiểm tra thiết kế phù hợp với quy trình sản xuất (DFM).

-

Yêu cầu các thông số kỹ thuật dựa trên tiêu chuẩn IPC. Sử dụng IPC-2226 và IPC-6016 khi có thể.

-

Lên kế hoạch bố trí các lớp mạch với đủ các lớp mặt đất để giữ cho đường dẫn trở về ngắn.

-

Hãy sử dụng kích thước lỗ microvia phù hợp với khả năng sản xuất của nhà máy PCB của bạn. Kích thước phổ biến: 3–5 mil, thường là 4 mil.

-

Hãy cố gắng tránh sử dụng các lỗ vias xếp chồng lên nhau trừ khi thực sự cần thiết. Các lỗ vias mù/chôn lấp xen kẽ thường dễ thực hiện hơn.

-

Nếu bạn chọn quy trình ép laminate HDI nhiều bước, hãy chuẩn bị cho việc có thêm các bước gia công và kiểm tra.

-

Sử dụng mô phỏng phù hợp cho các thiết kế tốc độ cao hoặc tần số vô tuyến (RF) để kiểm tra nhiễu điện từ (EMI) và tính toàn vẹn tín hiệu.

-

Đối với cấu trúc phân nhánh BGA, các lỗ vi mạch (microvias) và thiết kế pad-in-pad giúp giảm diện tích phân nhánh và chiều dài đường dẫn.

-

Để kiểm soát chi phí, hãy giảm số bước ép màng khi có thể. Tối ưu hóa thông qua việc bố trí.

Tóm tắt kết luận

Bảng mạch HDI là loại bảng mạch in (PCB) có mật độ kết nối cao, sử dụng các lỗ vi mạch ẩn và chìm. Chúng cho phép các nhà thiết kế bố trí nhiều đường dẫn và linh kiện hơn trong không gian hẹp hơn. Quá trình định tuyến HDI đòi hỏi kế hoạch xếp lớp cẩn thận, các lớp mặt đất tốt, việc sử dụng lỗ vi mạch chính xác và các kiểm tra DFM phù hợp. HDI mang lại những lợi ích rõ rệt về kích thước, tốc độ tín hiệu và hiệu suất. HDI được ứng dụng trong nhiều lĩnh vực, từ y tế và di động đến ô tô và hàng không vũ trụ. Cấp độ HDI càng phức tạp, quy trình sản xuất càng tiên tiến và chi phí càng cao. Thiết kế tốt và giao tiếp sớm với nhà cung cấp sẽ giúp bạn có được bảng mạch HDI phù hợp cho sản phẩm của mình.

Câu hỏi thường gặp

Microvias là các lỗ vias rất nhỏ (thường được khoan bằng laser) chỉ kết nối các lớp liền kề. Lỗ vias mù kết nối các lớp ngoài với các lớp trong; lỗ vias chìm chỉ kết nối các lớp trong. Các loại lỗ vias này giúp tiết kiệm không gian trên bảng mạch và cải thiện việc định tuyến.

Những lợi ích chính: mật độ linh kiện cao hơn, đường truyền tín hiệu ngắn hơn (đảm bảo tính toàn vẹn tín hiệu tốt hơn), sản phẩm nhỏ gọn và nhẹ hơn, cùng với việc bố trí mạch được cải thiện cho các chip BGA có khoảng cách chân nhỏ và mạch tốc độ cao.

Các ứng dụng phổ biến: điện thoại thông minh và thiết bị di động, thiết bị 5G và mạng, thiết bị y tế, hàng không vũ trụ, điện tử ô tô và các sản phẩm tiêu dùng nhỏ gọn.

Các quy tắc quan trọng: giới hạn đường kính và khoảng cách giữa các lỗ microvia, kiểm soát độ dày và trở kháng của vật liệu điện môi, lập kế hoạch cho các đường thoát BGA (cấu trúc phân nhánh hình xương chó) và tránh sử dụng lỗ via nằm trong pad trừ khi đã được lấp đầy hoặc làm phẳng đúng cách. Tuân thủ các nguyên tắc DFM và ma trận khả năng của nhà sản xuất.