1. Định nghĩa và khi nào nên thêm lớp

Cho Bo mạch đa lớp tốc độ cao, Một thiết kế hai lớp cơ bản thường không thể đáp ứng yêu cầu về chất lượng tín hiệu và mật độ đường dẫn. Trong trường hợp đó, bạn cần thêm các lớp vào cấu trúc PCB để đáp ứng yêu cầu thiết kế.

2. Mặt phẳng dương (tín hiệu) và mặt phẳng âm (ngược)

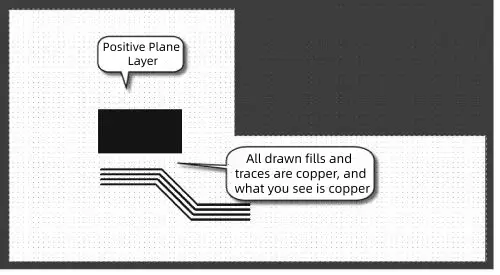

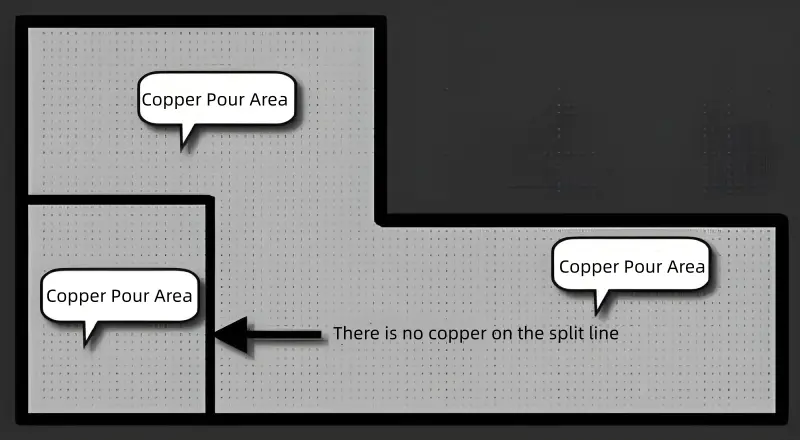

Mặt phẳng dương là lớp tín hiệu thông thường được sử dụng cho việc định tuyến. Các phần nhìn thấy được là các đường dẫn đồng. Trên mặt phẳng dương, bạn có thể thực hiện các vùng đổ đồng lớn và lấp đầy các khu vực bằng đồng, ví dụ như sử dụng các thuật ngữ như “đường dẫn” hoặc “đồng” để mô tả các khu vực đồng. Xem Hình 8-32.

Mặt phẳng âm là ngược lại. Với mặt phẳng âm, mặc định là phủ đồng trên toàn bộ lớp. Các khu vực định tuyến là các vùng cắt. Không có đồng trên các đường định tuyến. Điều bạn làm là cắt bỏ đồng và sau đó đặt các mạng cho các vùng đã cắt. Xem Hình 8-33.

3. Tách các mặt phẳng nguồn/đất bên trong

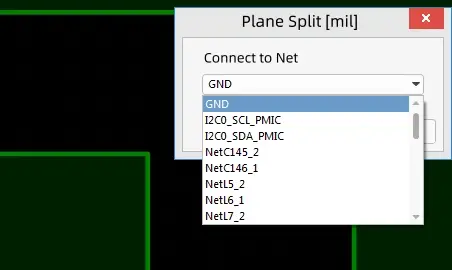

Trong các phiên bản cũ của Protel, các lớp nguồn bên trong được chia tách bằng chức năng “split”. Trong các phiên bản hiện tại như Altium Designer 19, Bạn chia bằng cách vẽ “đường thẳng” và sử dụng phím tắt “PL” để đặt chúng. Các đường chia không nên quá mỏng. Bạn có thể chọn 15 mil hoặc lớn hơn. Khi đổ đồng sau khi chia, vẽ một đa giác đóng bằng công cụ “đường thẳng”, sau đó nhấp đúp vào bên trong đa giác và thiết lập mạng cho việc đổ đồng. Xem Hình 8-34.

Cả mặt phẳng dương và âm đều có thể được sử dụng cho các lớp nguồn hoặc lớp đất bên trong. Bạn cũng có thể tạo ra một mặt phẳng dương bên trong bằng cách định tuyến và đổ đồng. Ưu điểm của mặt phẳng âm là bạn bắt đầu với một khu vực đồng lớn được đổ sẵn. Sau đó, bạn có thể thêm các lỗ vias hoặc thay đổi kích thước đổ đồng mà không cần đổ lại toàn bộ lớp. Điều này giúp tiết kiệm thời gian trong việc tính toán lại việc đổ đồng. Khi các lớp bên trong được sử dụng làm lớp nguồn và lớp đất (cũng được gọi là lớp đất hoặc lớp trở), các lớp này chủ yếu là các khu vực đồng lớn được đổ sẵn. Ưu điểm của việc sử dụng mặt phẳng âm ở đây là rõ ràng.

4. Hiểu về cấu trúc lớp của bảng mạch in (PCB)

Khi các mạch điện tốc độ cao trở nên phổ biến hơn, độ phức tạp của PCB cũng tăng lên. Để tránh nhiễu điện từ, các lớp tín hiệu và lớp nguồn phải được tách biệt. Điều này dẫn đến thiết kế PCB nhiều lớp. Trước khi thiết kế PCB đa lớp, nhà thiết kế phải xác định cấu trúc bảng mạch dựa trên kích thước mạch, kích thước bảng mạch và yêu cầu tương thích điện từ (EMC). Nói cách khác, quyết định sử dụng bảng mạch 4 lớp, 6 lớp hay nhiều lớp hơn. Đây là ý tưởng cơ bản của thiết kế bảng mạch đa lớp.

Sau khi quyết định số lượng lớp, bước tiếp theo là đặt các lớp nguồn và lớp đất bên trong, đồng thời quyết định cách phân phối các loại tín hiệu khác nhau trên các lớp đó. Lựa chọn này được gọi là lựa chọn cấu trúc xếp lớp (stackup selection). Cấu trúc xếp lớp là một yếu tố quan trọng ảnh hưởng đến hiệu suất EMC của PCB. Một thiết kế xếp chồng tốt có thể giảm đáng kể nhiễu điện từ (EMI) và nhiễu chéo..

Không phải lúc nào nhiều lớp cũng tốt hơn, và không phải lúc nào ít lớp cũng tốt hơn. Việc lựa chọn cấu trúc nhiều lớp đòi hỏi phải xem xét nhiều yếu tố. Từ góc độ thiết kế mạch, nhiều lớp giúp việc bố trí mạch dễ dàng hơn. Tuy nhiên, chi phí sản xuất và độ phức tạp cũng tăng lên. Đối với nhà sản xuất, Việc xếp chồng các lớp có đối xứng hay không là một vấn đề quan trọng trong quá trình sản xuất. Do đó, số lượng lớp phải được cân đối để đáp ứng tất cả các yêu cầu.

Các nhà thiết kế có kinh nghiệm thường thực hiện việc bố trí sơ bộ các thành phần. Sau đó, họ phân tích các điểm nghẽn trong quá trình định tuyến. Họ tính toán các yêu cầu định tuyến đặc biệt, chẳng hạn như cặp tín hiệu vi sai và các mạng nhạy cảm. Từ đó, họ quyết định số lượng lớp tín hiệu cần thiết. Sau đó, họ xác định số lượng lớp nguồn/đất bên trong dựa trên loại nguồn, yêu cầu cách ly và khả năng chống nhiễu. Sau bước này, tổng số lớp của bảng mạch cơ bản đã được xác định.

5. Cấu trúc lớp PCB thông dụng

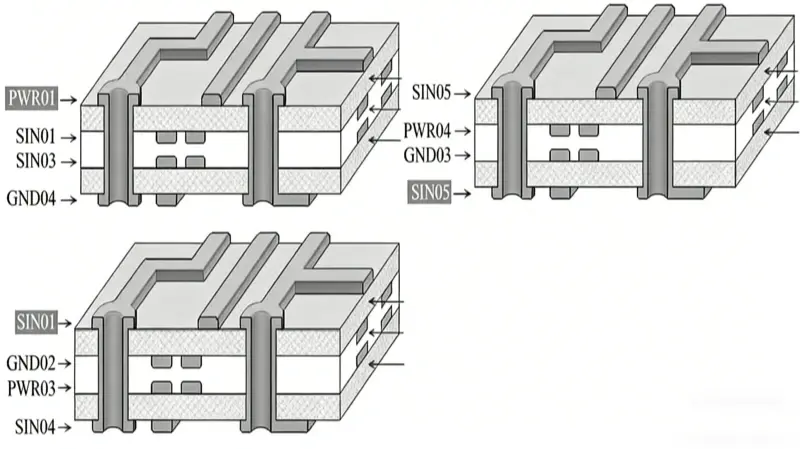

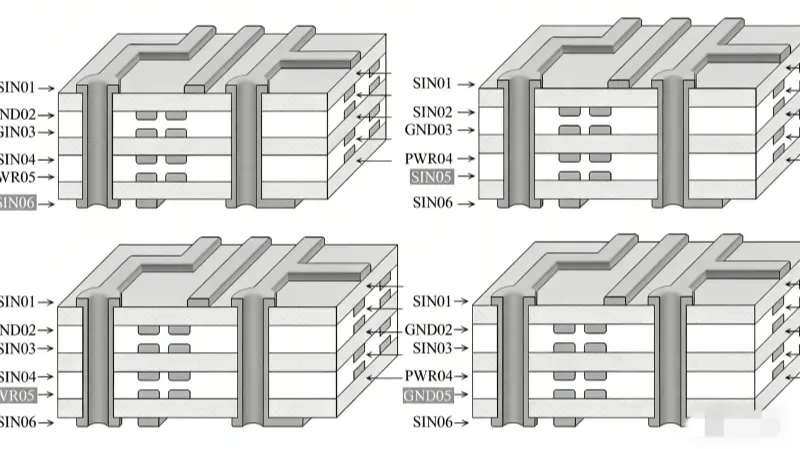

Sau khi số lượng lớp đã được xác định, công việc tiếp theo là sắp xếp thứ tự của các lớp đó. Hình 8-35 và 8-36 minh họa các cấu trúc xếp lớp thông dụng cho bảng mạch 4 lớp và 6 lớp.

6. Phân tích xếp chồng

Cách xếp chồng như thế nào? Loại xếp chồng nào tốt hơn? Hãy tuân theo các quy tắc cơ bản sau:

Khi có thể, hãy biến mặt linh kiện và mặt hàn thành các mặt đất hoàn toàn (điều này cung cấp khả năng chắn sóng).

Tránh sử dụng các lớp đường dẫn song song liền kề càng nhiều càng tốt.

Đặt tất cả các lớp tín hiệu gần mặt đất khi có thể.

Đặt các tín hiệu quan trọng gần lớp đất và tránh đi qua các khu vực bị chia cắt.

Áp dụng các quy tắc này vào các ví dụ xếp chồng thông thường được hiển thị trong Hình 8-35 và 8-36. Phân tích như sau.

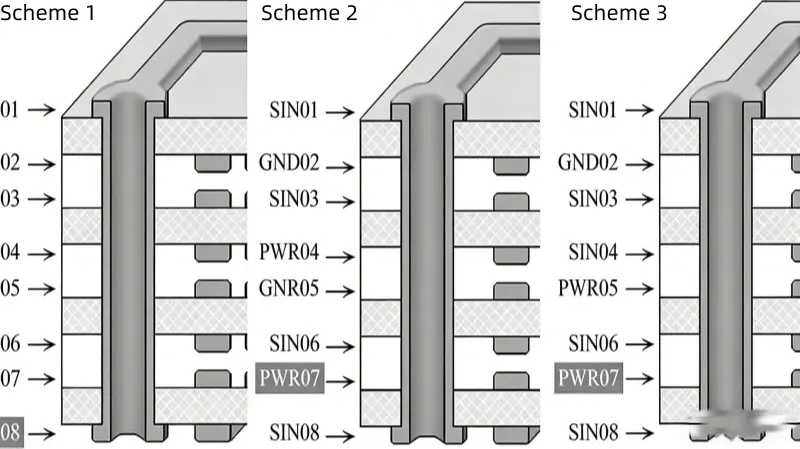

(1) Bảng 8-1 so sánh ưu nhược điểm của ba phương án xếp lớp bảng mạch 4 lớp phổ biến.

| Phương án | Sơ đồ hệ thống (Nghệ thuật ASCII) | Ưu điểm | Nhược điểm |

|---|---|---|---|

| Phương án 1 | ┌─────────────────────┐ │ PWR01 (Nguồn) │ ├─────────────────────┤ │ SIN02 (Dấu hiệu) │ ├─────────────────────┤ │ SIN03 (Tín hiệu) │ ├─────────────────────┤ │ GND04 (Đất) │ └─────────────────────┘ | Phương án này chủ yếu được thiết kế để đạt được hiệu quả che chắn một lớp, với lớp nguồn và lớp đất được đặt lần lượt ở các lớp trên và dưới. | (1) Các lớp nguồn và lớp đất cách nhau quá xa, dẫn đến trở kháng quá cao trên lớp nguồn;(2) Các lớp nguồn và lớp đất không hoàn chỉnh do ảnh hưởng của các pad linh kiện và các yếu tố khác;(3) Lớp tham chiếu không hoàn chỉnh gây ra các đường tín hiệu gián đoạn, khiến việc đạt được hiệu quả chắn nhiễu mong đợi trở nên khó khăn. |

| Phương án 2 | ┌─────────────────────┐ │ SIN01 (Dấu hiệu) │ ├─────────────────────┤ │ GND02 (Đất) │ ├─────────────────────┤ │ PWR03 (Nguồn) │ ├─────────────────────┤ │ SIN04 (Dấu hiệu) │ └─────────────────────┘ | Một lớp nền được đặt dưới mặt linh kiện, phù hợp cho các trường hợp linh kiện chính được đặt trên lớp trên cùng hoặc các tín hiệu quan trọng được bố trí trên lớp trên cùng. | / |

| Phương án 3 | ┌─────────────────────┐ │ SIN01 (Dấu hiệu) │ ├─────────────────────┤ │ PWR02 (Nguồn) │ ├─────────────────────┤ │ GND03 (Đất) │ ├─────────────────────┤ │ SIN04 (Tín hiệu) │ └─────────────────────┘ | Tương tự như Phương án 2, phương án này phù hợp cho các trường hợp các thành phần chính được đặt trên lớp dưới cùng hoặc các tín hiệu quan trọng được dẫn trên lớp dưới cùng. | / |

(2) Bảng 8-2 so sánh ưu nhược điểm của bốn phương án xếp lớp bảng mạch 6 lớp phổ biến.

| Phương án | Sơ đồ hệ thống (Nghệ thuật ASCII) | Ưu điểm | Nhược điểm |

|---|---|---|---|

| Phương án 1 | ┌─────────────────────┐ │ SIN01 (Dấu hiệu) │ ├─────────────────────┤ │ GND02 (Đất) │ ├─────────────────────┤ │ SIN03 (Tín hiệu) │ ├─────────────────────┤ │ SIN04 (Tín hiệu) │ ├─────────────────────┤ │ PWR05 (Nguồn) │ ├─────────────────────┤ │ SIN06 (Tín hiệu) │ └─────────────────────┘ | Sử dụng 4 lớp tín hiệu và hai lớp nguồn/đất bên trong, cung cấp thêm các lớp tín hiệu để thuận tiện cho việc bố trí mạch giữa các thành phần. | (1) Mặt phẳng nguồn và mặt phẳng đất cách nhau quá xa, dẫn đến độ kết nối không đủ;(2) Các lớp tín hiệu SIN03 và SIN04 chủ yếu được bố trí trên các lớp bề mặt, gây ra tình trạng cách ly tín hiệu kém và nhiễu chéo, đòi hỏi phải bố trí xen kẽ. |

| Phương án 2 | ┌─────────────────────┐ │ SIN01 (Dấu hiệu) │ ├─────────────────────┤ │ SIN02 (Dấu hiệu) │ ├─────────────────────┤ │ GND03 (Đất) │ ├─────────────────────┤ │ PWR04 (Nguồn) │ ├─────────────────────┤ │ SIN05 (Tín hiệu) │ ├─────────────────────┤ │ SIN06 (Tín hiệu) │ └─────────────────────┘ | Mặt phẳng nguồn và mặt phẳng đất được kết nối hoàn toàn. | Các lớp tín hiệu bề mặt liền kề cũng là các lớp tín hiệu, dẫn đến cách ly tín hiệu kém và nhiễu chéo. |

| Phương án 3 | ┌─────────────────────┐ │ SIN01 (Dấu hiệu) │ ├─────────────────────┤ │ GND02 (Đất) │ ├─────────────────────┤ │ SIN03 (Dấu hiệu) │ ├─────────────────────┤ │ GND04 (Đất) │ ├─────────────────────┤ │ PWR05 (Nguồn) │ ├─────────────────────┤ │ SIN06 (Tín hiệu) │ └─────────────────────┘ | (1) Mặt phẳng nguồn và mặt phẳng đất được kết nối hoàn toàn;(2) Mỗi lớp tín hiệu nằm liền kề với mặt phẳng nguồn/đất bên trong, cung cấp cách ly hiệu quả với các lớp tín hiệu khác và giảm nhiễu chéo;(3) Lớp tín hiệu SIN03 nằm liền kề với hai mặt phẳng bên trong (GND02 và PWR05), có thể bảo vệ hiệu quả SIN03 khỏi nhiễu từ bên ngoài và giảm nhiễu chéo từ SIN03 sang các lớp khác. | / |

| Phương án 4 | ┌─────────────────────┐ │ SIN01 (Dấu hiệu) │ ├─────────────────────┤ │ GND02 (Đất) │ ├─────────────────────┤ │ PWR03 (Nguồn) │ ├─────────────────────┤ │ GND04 (Đất) │ ├─────────────────────┤ │ PWR05 (Nguồn) │ ├─────────────────────┤ │ SIN06 (Dấu hiệu) │ └─────────────────────┘ | (1) Mặt phẳng nguồn và mặt phẳng đất được kết nối hoàn toàn;(2) Mỗi lớp tín hiệu nằm liền kề với mặt phẳng nguồn/đất bên trong, cung cấp cách ly hiệu quả với các lớp tín hiệu khác và giảm nhiễu chéo. | / |

Khi so sánh các phương án từ 1 đến 4, nếu hiệu suất tín hiệu là ưu tiên hàng đầu, các phương án 3 và 4 rõ ràng tốt hơn hai phương án đầu tiên. Tuy nhiên, trong thiết kế sản phẩm thực tế, chi phí là một yếu tố quan trọng. Với mật độ đường dẫn cao, các nhà thiết kế thường chọn phương án 1 cho cấu trúc lớp để tiết kiệm chi phí. Khi thực hiện đường dẫn trên phương án 1, cần chú ý đặc biệt đến các điểm giao nhau giữa hai lớp tín hiệu liền kề và cố gắng giảm nhiễu chéo (crosstalk) càng nhiều càng tốt.

(3) Đối với các bảng mạch 8 lớp thông thường, các tùy chọn xếp lớp được khuyến nghị được hiển thị trong Hình 8-37. Nên chọn tùy chọn 1 hoặc tùy chọn 2. Tùy chọn 3 có thể sử dụng được.

7. Thêm và chỉnh sửa lớp

Sau khi xác nhận kế hoạch xếp chồng, làm thế nào để thêm các lớp trong Altium Designer? Dưới đây là một ví dụ đơn giản.

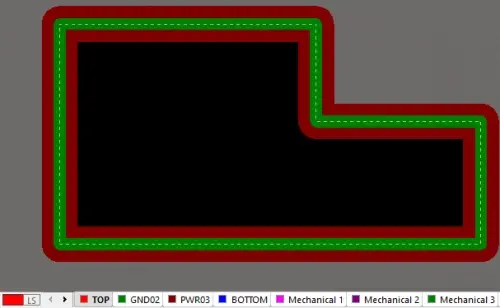

Chạy lệnh menu “Thiết kế → Quản lý chồng lớp” hoặc nhấn phím tắt “DK” để mở cửa sổ Quản lý chồng lớp. Cài đặt các thông số liên quan như minh họa trong Hình 8-38.

Nhấp chuột phải và chọn “Chèn lớp ở trên” hoặc “Chèn lớp ở dưới” để thêm một lớp. Bạn có thể thêm một mặt phẳng dương hoặc một mặt phẳng âm. Sử dụng “Di chuyển lớp lên” hoặc “Di chuyển lớp xuống” để điều chỉnh thứ tự của các lớp đã thêm.

Nhấp đúp vào tên lớp để đổi tên nó. Bạn có thể đặt tên cho các lớp là TOP, GND02, SIN03, SIN04, PWR05, BOTTOM, v.v. Altium Designer 19 hỗ trợ cách đặt tên “chữ cái + số lớp” này. Điều này giúp việc đọc và nhận diện dễ dàng hơn.

Điều chỉnh độ dày của bảng mạch và lớp theo cấu trúc xếp chồng.

Để đáp ứng yêu cầu 20H của thiết kế, bạn có thể đặt khoảng cách giữ lại (khoảng cách lệch trong) của mặt phẳng âm. [Lưu ý: Văn bản gốc sử dụng “20H.” Người dịch giữ nguyên thuật ngữ này như trong bản gốc.]

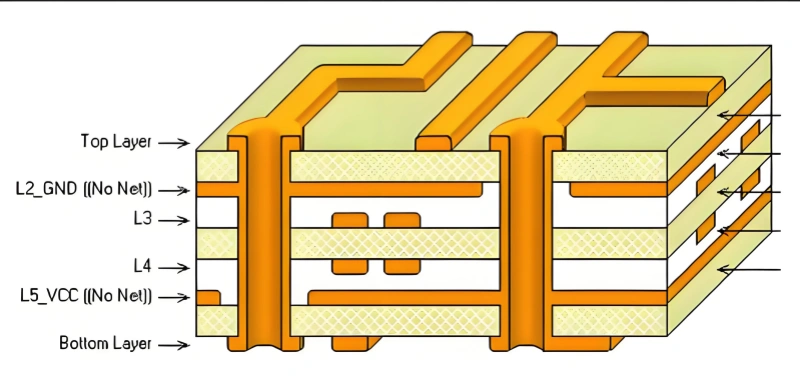

Nhấp vào “OK” để hoàn tất cài đặt xếp chồng. Hiệu ứng xếp chồng của một bảng mạch 4 lớp được minh họa trong Hình 8-39.

8. Khuyến nghị

Đề xuất xem các lớp tín hiệu như các mặt phẳng dương và xem các lớp nguồn và mặt đất như các mặt phẳng âm. Phương pháp này có thể giảm đáng kể kích thước dữ liệu tệp và tăng tốc quá trình thiết kế.