Lỗ via là một trong những thành phần quan trọng của bảng mạch in nhiều lớp (PCB). Trong nhiều loại bảng mạch, chi phí khoan chiếm khoảng 30% đến 40% tổng chi phí sản xuất bảng mạch. Nói một cách đơn giản, bất kỳ lỗ nào trên PCB đều có thể được gọi là lỗ via. Về chức năng, lỗ via có hai công dụng chính: một là tạo kết nối điện giữa các lớp, và hai là cố định hoặc định vị các linh kiện.

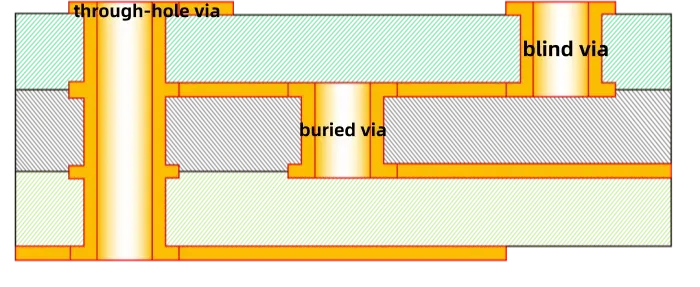

Nếu xem xét quy trình sản xuất, các lỗ vias có thể được phân thành ba loại: lỗ vias mù, lỗ vias chìm và lỗ vias xuyên qua (lỗ vias xuyên lỗ). Lỗ vias mù bắt đầu từ bề mặt trên hoặc dưới của bảng mạch in (PCB) và đi xuống một lớp bên trong nào đó. Nó có độ sâu nhất định và được sử dụng để kết nối các đường dẫn trên bề mặt với các đường dẫn ở lớp bên trong. Độ sâu của lỗ vias mù thường không vượt quá một tỷ lệ nhất định so với đường kính lỗ. Lỗ via chôn ngầm là lỗ chỉ kết nối các lớp bên trong; nó không tiếp xúc với bất kỳ bề mặt nào của bảng mạch. Cả lỗ via mù và lỗ via chôn ngầm đều được tạo ra bên trong bảng mạch trước khi ép laminate, và chúng có thể chồng lên nhiều lớp bên trong trong quá trình hình thành. Loại thứ ba là lỗ thông (through via). Lỗ này xuyên suốt toàn bộ bảng mạch. Nó có thể được sử dụng cho các kết nối nội bộ hoặc làm lỗ lắp đặt hoặc định vị cho các linh kiện. Vì lỗ thông dễ chế tạo và rẻ hơn, hầu hết các bảng mạch in đều sử dụng chúng thay vì lỗ mù hoặc lỗ chôn. Trong phần còn lại của văn bản này, trừ khi có quy định khác, từ “via” đề cập đến lỗ thông.

Thông qua cấu trúc và lý do tại sao quy mô lại quan trọng

Từ góc độ thiết kế, một lỗ via bao gồm hai phần chính. Một là lỗ khoan ở giữa. Phần còn lại là vùng pad xung quanh lỗ khoan. Kích thước của hai phần này quyết định kích thước của lỗ via. Khi một bảng mạch in (PCB) yêu cầu tốc độ cao và mật độ cao, các nhà thiết kế thường muốn các lỗ via có kích thước nhỏ nhất có thể. Các lỗ via nhỏ giúp tiết kiệm không gian cho việc bố trí đường mạch trên bảng. Ngoài ra, các lỗ via nhỏ hơn có điện dung ký sinh thấp hơn, do đó phù hợp hơn với các mạch tốc độ cao.

Tuy nhiên, việc thu nhỏ kích thước lỗ via sẽ làm tăng chi phí. Hơn nữa, kích thước lỗ via không thể thu nhỏ vô hạn. Giới hạn này xuất phát từ các quy trình khoan và mạ. Lỗ càng nhỏ, thời gian khoan càng lâu và mũi khoan càng dễ bị lệch tâm. Ngoài ra, khi độ sâu lỗ lớn hơn sáu lần đường kính mũi khoan, rất khó để đảm bảo thành lỗ được mạ đồng đều. Ví dụ, một PCB sáu lớp thông thường có độ dày (độ sâu lỗ via) khoảng 50 mil. Trong điều kiện đó, nhà máy sản xuất PCB thường có thể khoan xuống đường kính tối thiểu khoảng 8 mil.

Điện dung ký sinh của lỗ thông

Một lỗ via có điện dung ký sinh với mặt đất. Nếu biết đường kính lỗ thông qua mặt đất trên lớp đồng là D2, đường kính đế lỗ via là D1, độ dày bảng mạch in (PCB) là T và hằng số điện môi của chất nền bảng mạch là ε, thì điện dung ký sinh xấp xỉ của lỗ via là:

C = 1,41 × ε × T × D1 / (D2 − D1)

Công thức này cho phép ước tính hợp lý điện dung của lỗ thông. Điện dung phụ chủ yếu làm tăng thời gian tăng của tín hiệu, từ đó làm giảm tốc độ hoạt động của mạch.

Hãy lấy một ví dụ cụ thể. Giả sử độ dày bảng mạch là 50 mil. Đường kính trong của lỗ via là 10 mil và đường kính pad là 20 mil. Khoảng cách giữa pad và vùng đồng nối đất là 32 mil. Áp dụng công thức trên và lấy ε = 4,4, ta có:

C = 1,41 × 4,4 × 0,050 × 0,020 / (0,032 − 0,020) ≈ 0,517 pF

Độ lớn của điện dung này làm thay đổi thời gian tăng. Nếu trở kháng đặc trưng là 55 ohm, sự thay đổi thời gian tăng của mạch 10%–90% do điện dung này gây ra là khoảng:

T10−90 = 2,2 × C × (Z0 / 2) ≈ 2,2 × 0,517 × (55 / 2) ≈ 31,28 ps

Từ những con số này, chúng ta thấy rằng điện dung ký sinh của một lỗ via duy nhất chỉ có ảnh hưởng nhỏ đến thời gian tăng. Tuy nhiên, nếu tín hiệu đi qua nhiều lỗ via khi chuyển lớp, các tác động này sẽ cộng dồn lại. Do đó, nhà thiết kế cần phải cân nhắc kỹ lưỡng vấn đề này.

Điện cảm ký sinh của lỗ thông

Ngoài điện dung phụ, lỗ via còn có điện cảm phụ. Trong thiết kế mạch số tốc độ cao, tác động tiêu cực từ điện cảm phụ của lỗ via thường lớn hơn so với điện dung phụ. Điện cảm nối tiếp của lỗ via có thể làm suy yếu tác dụng của các tụ điện bypass và làm giảm hiệu suất lọc của toàn bộ hệ thống nguồn.

Một công thức gần đúng đơn giản để tính điện cảm của lỗ dẫn là:

L = 5,08 × h × [ ln(4h / d) + 1 ]

trong đó:

- L là điện cảm của đường dẫn,

- h là chiều dài đường dẫn,

- d là đường kính mũi khoan định tâm.

Từ công thức, chúng ta thấy rằng đường kính lỗ via có ảnh hưởng nhỏ đến độ tự cảm, trong khi chiều dài lỗ via có ảnh hưởng lớn nhất. Áp dụng ví dụ trên với h = 0,050 và d = 0,010, ta có:

L = 5,08 × 0,050 × [ ln(4 × 0,050 / 0,010) + 1 ] ≈ 1,015 nH

Nếu thời gian tăng của tín hiệu là 1 ns, thì điện kháng cảm ứng tương đương là:

XL = π × L / T10−90 ≈ π × 1,015 nH / 1 ns ≈ 3,19 Ω

Khi có dòng điện tần số cao, không thể bỏ qua mức trở kháng này. Cũng cần lưu ý rằng tụ điện bypass được đặt để nối lớp nguồn với lớp đất thường cần hai lỗ vias. Điều đó có nghĩa là độ tự cảm của lỗ vias sẽ tăng gấp đôi đối với đường dẫn bypass này.

Điều này có ý nghĩa như thế nào đối với thiết kế tốc độ cao

Từ phân tích trên về các hiện tượng điện dung và điện trở phụ của lỗ via, chúng ta có thể thấy rằng một lỗ via tưởng chừng đơn giản cũng có thể gây ra những tác động tiêu cực nghiêm trọng trên bảng mạch in tốc độ cao. Để giảm thiểu những vấn đề này, các nhà thiết kế có thể áp dụng các biện pháp sau đây.

- Chọn kích thước hộp phù hợp

Hãy cân nhắc cả chi phí lẫn chất lượng tín hiệu. Ví dụ, đối với bảng mạch in (PCB) của mô-đun bộ nhớ có từ 6 đến 10 lớp, việc chọn lỗ vias có kích thước 10/20 mil (lỗ khoan/điểm tiếp xúc) là lựa chọn phù hợp. Đối với một số bảng mạch nhỏ, mật độ cao, bạn có thể thử sử dụng lỗ vias kích thước 8/18 mil. Với công nghệ hiện tại, rất khó để chế tạo lỗ vias nhỏ hơn kích thước đó. Đối với lỗ vias cấp nguồn hoặc nối đất, hãy sử dụng kích thước lớn hơn để giảm trở kháng. - Nếu có thể, hãy sử dụng tấm ván mỏng hơn

Như các công thức cho thấy, một tấm mạch mỏng hơn giúp giảm cả điện dung và điện cảm của các lỗ thông. - Tránh thay đổi lớp không cần thiết

Hãy cố gắng dẫn tín hiệu mà không cần chuyển lớp. Nói cách khác, hãy sử dụng càng ít lỗ vias càng tốt. - Đặt các chân nguồn và chân nối đất gần các lỗ thông

Đặt các chân nguồn và chân đất gần các lỗ vias tương ứng. Giữ cho đường dẫn giữa lỗ vias và chân càng ngắn càng tốt, vì đường dẫn dài sẽ làm tăng độ tự cảm. Sử dụng đường dẫn dày hơn cho nguồn và đất để giảm trở kháng. - Đặt các lỗ vias nối đất gần các lỗ vias chuyển đổi lớp tín hiệu

Hãy đặt các lỗ nối đất gần các lỗ nối ở những vị trí tín hiệu chuyển lớp. Điều này giúp tín hiệu có đường dẫn trở về gần đó. Bạn cũng có thể thêm nhiều lỗ nối đất bổ sung nếu cần thiết. Tuy nhiên, hãy linh hoạt. Mô hình lỗ nối được đề cập trước đó giả định có một điểm tiếp xúc trên mỗi lớp. Trong một số trường hợp, bạn có thể giảm bớt hoặc loại bỏ các điểm tiếp xúc trên một số lớp bên trong. Khi mật độ lỗ nối rất cao, các điểm tiếp xúc lớn trên vùng đồng phủ có thể tạo thành một vòng lặp bị đứt đoạn. Để khắc phục điều này, bạn có thể di chuyển một số lỗ nối hoặc giảm kích thước các điểm tiếp xúc trên một số lớp nhất định.

Thiết kế mạch in tốc độ cao — những gợi ý thiết thực

Bảng mạch in tốc độ cao thường sử dụng nhiều lớp, và các lỗ vias là một yếu tố quan trọng trong thiết kế. Một lỗ via trên bảng mạch in bao gồm ba phần: chính lỗ đó, vùng tiếp xúc xung quanh lỗ, và vùng cách ly lớp nguồn (khoảng trống trên các lớp nguồn và lớp đất xung quanh lỗ via).

Dưới đây là một số lưu ý thực tiễn đối với bảng mạch đa lớp tốc độ cao:

- Dựa trên khuyến nghị về kích cỡ

Đối với các bảng mạch đa lớp thông thường có mật độ vừa phải, lỗ via có kích thước 0,25 mm / 0,51 mm / 0,91 mm (lỗ khoan / pad / cách ly nguồn) là một lựa chọn phù hợp. Đối với các bảng mạch có mật độ cao, kích thước 0,20 mm / 0,46 mm / 0,86 mm có thể phù hợp. Các lỗ via không mạ có thể được sử dụng trong một số thiết kế. Đối với các lỗ via nguồn hoặc đất, nên xem xét sử dụng kích thước lớn hơn để giảm trở kháng. - Khu vực cách ly nguồn điện

Khu vực cách ly nguồn càng rộng thì càng tốt. Cần xem xét mật độ lỗ via trên mặt phẳng. Thông thường, công thức D1 = D2 + 0,41 được sử dụng làm nguyên tắc hướng dẫn, có nghĩa là đường kính pad bằng đường kính khoảng trống trên mặt phẳng cộng thêm 0,41 mm. Điều này giúp đảm bảo khoảng trống trên mặt phẳng đủ rộng. - Giảm thiểu việc thay đổi lớp

Giảm số lượng lỗ thông bằng cách tránh thay đổi lớp không cần thiết trong quá trình định tuyến tín hiệu. - Sử dụng ván mỏng hơn

Các bảng mạch mỏng hơn giúp giảm cả điện dung và điện cảm của các lỗ vias. - Các kết nối nguồn/đất ngắn và rộng

Hãy đảm bảo đường dẫn từ lỗ via đến chân nguồn hoặc chân đất được nối ngắn. Hãy thiết kế các đường dẫn nguồn hoặc đất rộng nhất có thể để giảm trở kháng cảm ứng. - Nối đất qua các lỗ vias gần vị trí chuyển lớp

Thêm các lỗ nối đất gần các lỗ nối nơi tín hiệu di chuyển giữa các lớp. Điều này giúp tín hiệu có đường dẫn trở về ngắn.

Cũng cần lưu ý rằng chiều dài lỗ via là yếu tố chính quyết định độ tự cảm của lỗ via. Đối với các lỗ via xuyên qua lớp trên và lớp dưới, chiều dài lỗ via bằng toàn bộ độ dày của bảng mạch. Khi số lớp tăng lên, độ dày của bảng mạch có thể vượt quá 5 mm. Trong thiết kế tốc độ cao, chiều dài lỗ via thường được giữ dưới 2,0 mm để giảm thiểu các vấn đề liên quan đến lỗ via. Đối với chiều dài lỗ via lớn hơn 2,0 mm, việc tăng đường kính lỗ via có thể giúp khôi phục tính liên tục của trở kháng. Khi chiều dài lỗ via là 1,0 mm hoặc ít hơn, đường kính lỗ via tối ưu là khoảng 0,20 mm đến 0,30 mm.

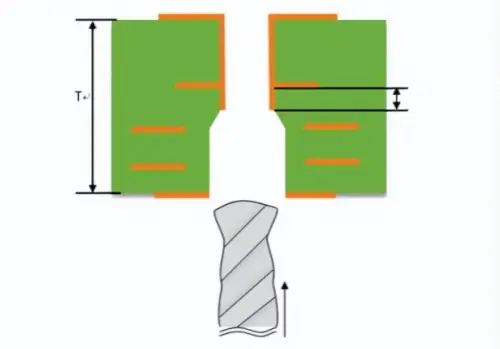

Khoan ngược trong sản xuất PCB

1. Backdrilling là gì?

Khoan ngược là một bước khoan đặc biệt được sử dụng trên các bảng mạch lỗ sâu. Ví dụ, khi chế tạo một bảng mạch 12 lớp, chúng ta có thể muốn kết nối lớp 1 với lớp 9. Thông thường, chúng ta khoan một lỗ xuyên qua một lần rồi mới mạ. Lỗ via đó sẽ chạy từ lớp 1 đến lớp 12, nhưng chúng ta chỉ cần kết nối giữa lớp 1 và lớp 9. Phần thừa từ lớp 10 đến lớp 12 hoạt động như một đoạn thừa. Đoạn thừa này ảnh hưởng đến đường dẫn tín hiệu và có thể gây ra các vấn đề về tính toàn vẹn tín hiệu trong tín hiệu truyền thông. Để loại bỏ đoạn thừa này, chúng ta khoan nó từ mặt sau — một bước khoan thứ hai. Đây được gọi là khoan ngược. Trong thực tế, các nhà sản xuất không khoan hết từng chút một, vì các bước sau đó sẽ loại bỏ một phần đồng và mũi khoan có đầu nhọn. Vì vậy, nhà máy thường để lại một đoạn nhánh rất nhỏ. Chiều dài đoạn nhánh còn lại được gọi là giá trị B, và giá trị B tốt thường nằm trong khoảng từ 50 μm đến 150 μm.

2. Tại sao phải khoan ngược?

Kỹ thuật khoan ngược mang lại một số lợi ích:

- Nó giúp giảm tiếng ồn và nhiễu.

- Nó giúp cải thiện tính toàn vẹn tín hiệu.

- Nó có thể làm mỏng một vùng nhỏ trên bảng mạch.

- Điều này giúp giảm bớt nhu cầu sử dụng các lỗ thông mạch chìm hoặc lỗ thông mạch ẩn, từ đó làm giảm độ phức tạp của bảng mạch.

3. Quá trình khoan ngược có tác dụng gì?

Quá trình khoan ngược giúp loại bỏ phần lỗ thông qua (via) không đóng vai trò trong việc kết nối hoặc truyền tín hiệu. Điều này giúp ngăn chặn hiện tượng phản xạ, tán xạ, độ trễ và các tác động khác gây ra “sự biến dạng” tín hiệu. Các nghiên cứu cho thấy rằng ngoài thiết kế, vật liệu bảng mạch, đường truyền tín hiệu, đầu nối và bao bì chip, các lỗ thông qua (through vias) cũng có tác động lớn đến tính toàn vẹn tín hiệu.

4. Nguyên lý hoạt động của phương pháp khoan ngược

Phương pháp khoan ngược sử dụng mũi khoan được định vị bằng cách cảm biến bề mặt PCB. Khi đầu mũi khoan chạm vào lớp đồng trên bề mặt bảng mạch, một dòng điện vi mô sẽ được tạo ra. Dòng điện này cung cấp thông tin về độ cao bề mặt bảng mạch cho máy. Sau đó, máy sẽ khoan xuống đến độ sâu đã cài đặt và dừng lại.

5. Các bước của quy trình khoan ngược

Một quy trình khoan ngược điển hình có thể diễn ra như sau:

a. Tạo các lỗ định vị trên bảng mạch in (PCB). Sử dụng các lỗ này để thực hiện bước khoan đầu tiên (lỗ xuyên).

b. Sau khi khoan lần đầu, hãy mạ các lỗ. Trước khi mạ, hãy dùng màng bảo vệ khô để che các lỗ định vị nếu cần.

c. Vẽ mẫu lớp ngoài lên bảng mạch in.

d. Tiến hành mạ theo khuôn mẫu. Trước khi mạ theo khuôn mẫu, nếu cần, hãy xử lý lại các lỗ định vị bằng màng khô.

e. Sử dụng các lỗ đã khoan ở bước đầu tiên để định vị bảng mạch cho quá trình khoan ngược. Sử dụng mũi khoan để khoan bỏ các phần mạ cần khoan ngược.

f. Sau khi khoan lỗ phía sau, hãy rửa sạch các lỗ khoan để loại bỏ bụi khoan và cặn bẩn.

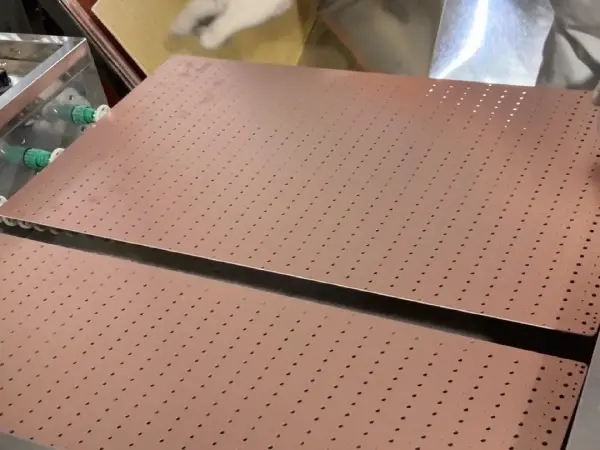

6. Các đặc tính kỹ thuật của bảng mạch khoan lỗ sau

Các tính năng kỹ thuật tiêu biểu bao gồm:

- Hầu hết các bảng mạch khoan lỗ sau đều là bảng mạch cứng.

- Số lớp thường dao động từ 8 đến 50 lớp.

- Độ dày của tấm ván thường là 2,5 mm trở lên.

- Tỷ lệ giữa độ dày và đường kính tương đối lớn.

- Kích thước của các tấm ván khá lớn.

- Đường kính tối thiểu ban đầu của mũi khoan thường là ≥ 0,3 mm.

- Số lượng đường mạch trên lớp ngoài rất ít; bảng mạch thường sử dụng mảng kẹp cho các lỗ lắp ép.

- Các lỗ khoan ngược thường lớn hơn 0,2 mm so với các lỗ cần loại bỏ.

- Dung sai độ sâu khoan ngược là khoảng ±0,05 mm.

- Nếu quá trình khoan ngược phải đi xuống đến lớp M, thì độ dày lớp điện môi từ lớp M đến lớp M−1 phải ít nhất là 0,17 mm.

7. Các ứng dụng điển hình của bảng mạch có lỗ khoan phía sau

Bảng mạch khoan lỗ sau chủ yếu được sử dụng trong các lĩnh vực đòi hỏi tính toàn vẹn tín hiệu cao và các hệ thống quy mô lớn. Các lĩnh vực phổ biến bao gồm thiết bị viễn thông, máy chủ quy mô lớn, thiết bị điện tử y tế, quân sự và hàng không vũ trụ. Do quân sự và hàng không vũ trụ là những lĩnh vực nhạy cảm, các bảng mạch nền cho các lĩnh vực này thường được sản xuất bởi các viện nghiên cứu, trung tâm R&D hoặc các nhà sản xuất PCB có nền tảng vững chắc trong các lĩnh vực đó. Tại Trung Quốc, phần lớn nhu cầu về bảng mạch nền đến từ ngành viễn thông, vốn đang phát triển nhanh chóng.

Tóm tắt

Tóm lại, các lỗ vias tuy đơn giản nhưng lại vô cùng quan trọng. Chúng kết nối các lớp mạch và đồng thời tạo ra điện dung và điện cảm phụ. Các yếu tố phụ này ảnh hưởng đến cả thời gian tăng của tín hiệu lẫn hiệu quả hoạt động của tụ điện bypass. Chiều dài của lỗ vias chủ yếu quyết định điện cảm. Kích thước lỗ vias, kích thước pad và khoảng cách an toàn ảnh hưởng đến điện dung. Đối với các thiết kế tốc độ cao, hãy tham khảo danh sách kiểm tra sau:

- Chọn kích thước lỗ vias phù hợp với mật độ và chi phí của bảng mạch. Đối với nhiều loại bảng mạch, kích thước 10/20 mil là phù hợp; đối với các bảng mạch có mật độ cao hơn, hãy thử kích thước 8/18 mil. Đối với các lỗ vias cấp nguồn/nối đất, hãy chọn kích thước lớn hơn.

- Nếu có thể, hãy sử dụng một tấm ván mỏng. Điều này giúp giảm thiểu các hiện tượng nhiễu do đường dẫn điện.

- Hãy tránh thay đổi lớp không cần thiết. Hãy duy trì đường dẫn trên cùng một lớp khi có thể.

- Đặt các chân nguồn và chân nối đất gần các lỗ vias và đảm bảo các đường nối ngắn và rộng.

- Thêm các lỗ nối đất gần các lỗ tín hiệu chuyển lớp để tạo ra đường dẫn hồi ngắn.

- Đối với các lỗ dẫn dài hoặc bảng mạch dày, hãy cân nhắc sử dụng phương pháp khoan ngược để loại bỏ các đoạn dây thừa gây ảnh hưởng xấu đến tín hiệu tốc độ cao.

- Khi mật độ đường dẫn rất cao, hãy cân nhắc giảm kích thước các pad trên một số lớp bên trong để tránh làm đứt các đường dẫn đồng.

Hãy tuân thủ các quy tắc này và xem xét toàn bộ hệ thống, chứ không chỉ tập trung vào một lỗ via duy nhất. Trong thiết kế mạch tốc độ cao, những chi tiết nhỏ cũng có thể tạo nên sự khác biệt. Một bản thiết kế lỗ via cẩn thận sẽ giúp mạch hoạt động hiệu quả hơn, giảm thiểu rủi ro và tiết kiệm thời gian khi gỡ lỗi sau này.