Trong thiết kế PCB, việc bố trí đường dẫn có thể được chia thành ba cấp độ chính. Cấp độ đầu tiên là kết nối cơ bản. Đây là yêu cầu cơ bản nhất trong thiết kế PCB. Nếu các mạch không được kết nối, bảng mạch sẽ không thể thực hiện chức năng cơ bản nào. Khi đó, bảng mạch đó chỉ là phế liệu. Đừng bàn đến những vấn đề khác.

Cấp độ thứ hai là hiệu suất. Đây là thước đo chất lượng của một bảng mạch in. Sau khi định tuyến, chúng ta phải xem xét cách đạt được hiệu suất tối ưu. Chúng ta phải tránh các loại nhiễu khác nhau. Đồng thời, chúng ta cũng phải đảm bảo tín hiệu ổn định và không bị nhiễu.

Cấp độ thứ ba là hình thức. Các đường mạch có thể được kết nối và bảng mạch có thể cho thấy hiệu suất điện tốt, nhưng bố cục vẫn có thể trông lộn xộn. Trong trường hợp đó, chúng ta nên sắp xếp các đường mạch sao cho gọn gàng. Việc bố trí đường mạch gọn gàng sẽ hỗ trợ cho quá trình kiểm tra và sửa chữa sau này. Điều này cũng thể hiện kỹ năng của một kỹ sư có kinh nghiệm.

Cách định tuyến hiệu quả

Các phương pháp bố trí đường dẫn có thể rất đa dạng. Để tránh các vấn đề như tín hiệu phản xạ khi các đường dẫn đầu vào và đầu ra chạy gần nhau và song song, cũng như tránh hiện tượng ghép nối phụ khi các đường dẫn trên hai lớp liền kề chạy song song, chúng ta cần xem xét nhiều yếu tố. Nếu nhiễu đủ mạnh, bảng mạch có thể hoàn toàn không hoạt động. Dưới đây là một số quy tắc được khuyến nghị cho việc bố trí đường dẫn trên PCB. Quy tắc “năm-năm” (quy tắc lựa chọn lớp)

Quy tắc này giúp xác định số lớp của bảng mạch in (PCB). Khi tần số đồng hồ đạt 5 MHz hoặc thời gian tăng của xung nhỏ hơn 5 ns, bảng mạch in (PCB) nên là bảng mạch nhiều lớp. Đây là một quy tắc phổ biến.

Đôi khi người ta vẫn chọn bảng mạch hai lớp vì lý do chi phí. Nếu bạn sử dụng bảng mạch hai lớp, hãy cố gắng dành toàn bộ một mặt làm mặt đất liên tục. Điều này sẽ giúp cải thiện hiệu suất.

Các nguyên tắc cơ bản về kết hợp tín hiệu số và tín hiệu tương tự

Hiện nay, nhiều bảng mạch in (PCB) đều có cả mạch số và mạch tương tự. Khi bố trí đường dẫn, cần lưu ý đến hiện tượng nhiễu giữa các mạch này, đặc biệt là nhiễu trên đường đất. Mạch số hoạt động ở tần số cao, trong khi mạch tương tự thường rất nhạy cảm.

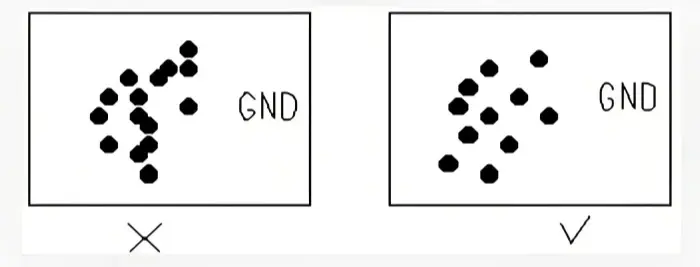

Đối với tín hiệu, hãy giữ các đường dẫn tần số cao cách xa các bộ phận tương tự nhạy cảm. Đối với đường nối đất, toàn bộ bảng mạch in (PCB) chỉ có một điểm nối với thế giới bên ngoài. Do đó, bạn phải xử lý việc nối đất cho các mạch số và tương tự bên trong bảng mạch một cách cẩn thận.

Trên bảng mạch, mặt đất kỹ thuật số và mặt đất tương tự thường được tách biệt và không kết nối với nhau. Chúng chỉ được nối với nhau tại điểm mà bảng mạch in (PCB) kết nối với thế giới bên ngoài, chẳng hạn như tại đầu nối. Hãy đảm bảo rằng mặt đất kỹ thuật số và mặt đất tương tự có một đường nối ngắn tại một điểm duy nhất. Một số hệ thống có thể chọn không dùng chung mặt đất trên bảng mạch. Hãy tuân thủ quyết định thiết kế của hệ thống.

Xử lý các đầu dây linh kiện trong các khu vực đồng có diện tích lớn

Các khu vực tiếp đất hoặc cấp nguồn bằng đồng có diện tích lớn thường kết nối với nhiều chân linh kiện. Để xử lý các chân linh kiện này, chúng ta phải cân bằng giữa hiệu suất điện và quá trình lắp ráp.

Từ góc độ điện, để đạt hiệu suất tối ưu, một pad cần được kết nối hoàn toàn với đồng. Tuy nhiên, các pad bằng đồng nguyên khối lại gây ra một số vấn đề trong quá trình hàn. Các vấn đề bao gồm:

Việc hàn cần rất nhiều nhiệt từ mỏ hàn.

Các mối hàn dễ bị lạnh hoặc yếu hơn.

Để cân bằng giữa nhu cầu điện và quá trình sản xuất, hãy sử dụng miếng đệm tản nhiệt. Một dạng phổ biến là miếng đệm hình chữ thập. Loại này được gọi là miếng đệm tản nhiệt hoặc miếng đệm nhiệt. Nó hỗ trợ quá trình hàn bằng cách cách ly nhiệt miếng đệm khỏi các mặt phẳng đồng lớn. Miếng đệm tản nhiệt giúp giảm nguy cơ xuất hiện các mối hàn lạnh. Đối với bảng mạch nhiều lớp, hãy xử lý các lỗ vias kết nối với các lớp nguồn và lớp đất theo cách tương tự.

Quy tắc hệ thống lưới

Hệ thống nối đất dạng lưới giúp giảm điện cảm đường dẫn và tạo ra đường dẫn hồi tốt cho dòng điện tần số cao. Tuy nhiên, cần lưu ý đến mật độ lưới.

Nếu lưới quá dày đặc, sẽ có nhiều bước lưới nhỏ. Điều này tạo ra một lượng lớn dữ liệu bố trí. Điều này đòi hỏi dung lượng lưu trữ lớn hơn và làm chậm các công cụ CAD. Ngoài ra, một số đường lưới trở nên vô dụng vì bị chiếm bởi các điểm tiếp xúc linh kiện hoặc lỗ lắp đặt. Nếu lưới quá thưa thớt, việc định tuyến sẽ trở nên khó khăn và tỷ lệ thành công của quá trình định tuyến sẽ giảm.

Vì vậy, hãy chọn mật độ lưới hợp lý. Khoảng cách tiêu chuẩn giữa các chân linh kiện là 0,1 inch (2,54 mm). Do đó, lưới cơ sở 0,1 inch hoặc các bội số nhỏ hơn của nó thường được sử dụng. Ví dụ: 0,05 inch, 0,025 inch, 0,02 inch, v.v.

Cách kiểm tra sau khi định tuyến

Sau khi hoàn tất việc bố trí mạch in (PCB), hãy kiểm tra xem thiết kế có tuân thủ các quy tắc và có đáp ứng các giới hạn sản xuất hay không. Các bước kiểm tra dưới đây là những bước thông thường.

Các nội dung cần kiểm tra bao gồm: các yếu tố trong bản vẽ thiết kế PCB tổng quát, kiểm tra điện của PCB, kiểm tra vật lý của PCB, các yếu tố thiết kế cơ khí, yêu cầu lắp đặt PCB, nhu cầu phân tách mạch, các vấn đề cơ khí, các vấn đề điện, đường dẫn và vị trí bố trí, chiều rộng và độ dày đường dẫn, khoảng cách giữa các đường dẫn, kiểm tra hình dạng đường dẫn, và danh sách các yếu tố thiết kế.

Danh sách kiểm tra thực tế

Kiểm tra xem khoảng cách giữa các lỗ vias có hợp lý không.

Kiểm tra xem chiều rộng của đường dẫn nguồn và đường dẫn nối đất có phù hợp với nhu cầu hiện tại hay không.

Kiểm tra xem các đường dẫn tín hiệu chính có tuân thủ các tiêu chuẩn tối ưu hay không (đường dẫn ngắn, trở kháng được kiểm soát, lớp chắn).

Kiểm tra xem các bộ phận analog và kỹ thuật số có được nối đất riêng biệt hay không, nếu cần.

Kiểm tra xem các đường mạch đồng được thêm vào trên bảng mạch có thể gây chập mạch tín hiệu hay không.

Kiểm tra xem bảng mạch có các đường kẻ hoặc dấu hiệu cần thiết cho nhà máy hay không.

Kiểm tra xem các cạnh của lớp nguồn và lớp đất trên bảng mạch nhiều lớp có độ lùi cần thiết hay không.

Nghiên cứu điển hình về định tuyến và các quy tắc chính

Việc bố trí đường mạch là một phần quan trọng trong thiết kế PCB. Quá trình này thường tốn nhiều thời gian nhất. Các kỹ sư nên tuân thủ các quy tắc cơ bản khi bố trí đường mạch, chẳng hạn như quy tắc vát cạnh và quy tắc 3W.

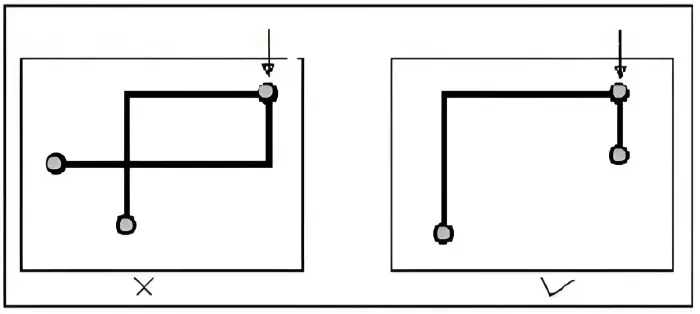

Quy tắc vòng lặp mặt đất

Nguyên tắc vòng lặp nhỏ nhất có nghĩa là diện tích được bao quanh bởi tín hiệu và đường dẫn trở về của nó phải càng nhỏ càng tốt. Diện tích vòng lặp càng nhỏ, bảng mạch sẽ càng ít phát xạ và càng ít nhận nhiễu từ bên ngoài.

Khi chia tách các mặt phẳng nối đất, hãy xem xét sự sắp xếp giữa hình dạng của mặt phẳng và các đường dẫn tín hiệu quan trọng. Tránh các vấn đề do các khe hở trên mặt phẳng nối đất gây ra, vì chúng làm tăng diện tích vòng lặp.

Trong các thiết kế hai lớp, hãy dành đủ diện tích cho nguồn điện. Lấp đầy phần không gian còn lại bằng đồng nối đất tham chiếu. Thêm các lỗ nối đất cần thiết để kết nối hai mặt của bảng mạch. Đối với các tín hiệu quan trọng, hãy sử dụng cách ly nối đất. Đối với các thiết kế tần số cao, hãy sử dụng bảng mạch nhiều lớp.

Quy tắc che chắn và bảo vệ

Việc che chắn là một phương pháp khác để giảm diện tích vòng lặp và giảm bức xạ. Nên sử dụng biện pháp che chắn cho các tín hiệu quan trọng như tín hiệu đồng hồ và tín hiệu đồng bộ.

Đối với các tín hiệu cực kỳ quan trọng hoặc có tần số rất cao, bạn có thể sử dụng lớp chắn bằng đồng hoặc thiết kế tương tự cáp đồng trục. Bao quanh đường dẫn tín hiệu ở tất cả các phía bằng đường nối đất. Đồng thời, hãy lên kế hoạch cho cách kết nối lớp chắn nối đất với mặt phẳng nối đất chính.

Quy tắc kiểm soát nhiễu chéo

Crosstalk là hiện tượng nhiễu giữa các mạng khác nhau trên bảng mạch in (PCB). Hiện tượng này xuất phát từ việc bố trí các đường dẫn song song có chiều dài lớn. Nguyên nhân là do điện dung và điện cảm phân bố giữa các đường dẫn song song.

Các phương pháp chính để chống nhiễu chéo:• Tăng khoảng cách giữa các đường dẫn song song. Tuân thủ quy tắc 3W.• Chèn các đường dẫn bảo vệ nối đất giữa các đường dẫn song song quan trọng.• Giảm khoảng cách giữa lớp định tuyến và mặt phẳng nối đất.

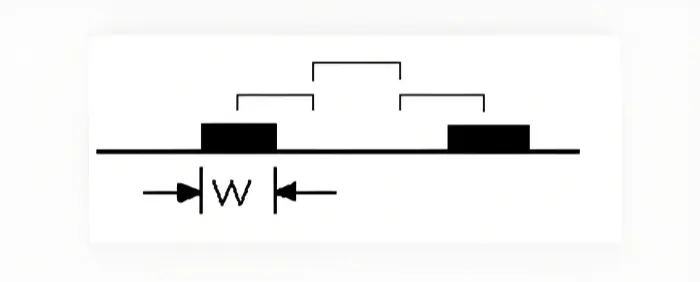

Nhắc nhở về quy tắc 3W

Để giảm nhiễu chéo, hãy giữ khoảng cách giữa các đường dẫn ở mức lớn. Nếu khoảng cách tâm gấp ba lần chiều rộng đường dẫn, khoảng 70% của vùng sẽ được cách ly. Để đạt mức cách ly 98%, hãy sử dụng 10W.

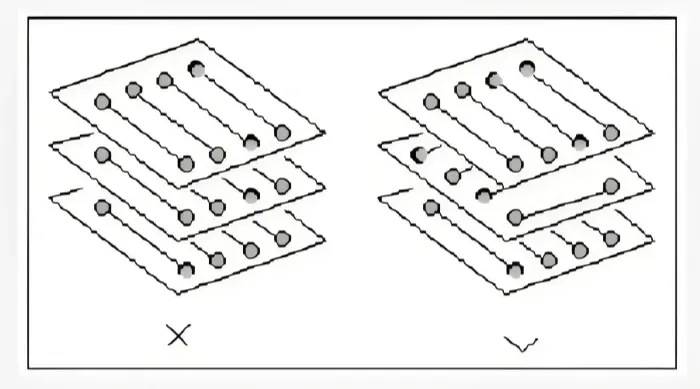

Kiểm soát hướng của các đường dẫn

Giữ cho hướng của các lớp liền kề vuông góc với nhau. Tránh bố trí các đường dẫn theo cùng một hướng trên các lớp liền kề. Điều này giúp giảm sự tương tác giữa các lớp. Nếu cấu trúc bảng mạch bắt buộc phải bố trí các đường dẫn song song, đặc biệt là trong các thiết kế tốc độ cao, hãy sử dụng các lớp mặt đất giữa các lớp bố trí để cách ly chúng. Ngoài ra, hãy sử dụng các đường dẫn bảo vệ nối đất giữa các đường dẫn tín hiệu.

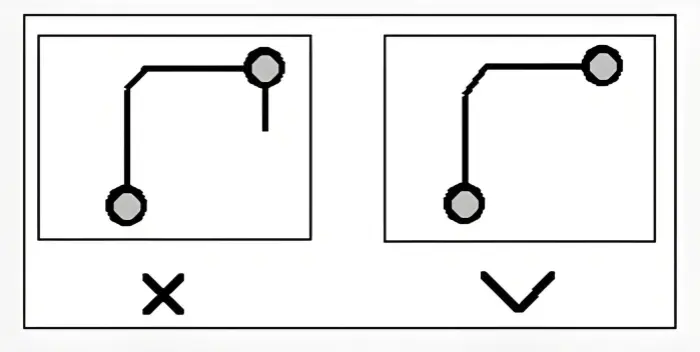

Quy tắc kiểm tra dấu vết treo

Không để bất kỳ đầu dây nào lơ lửng mà không được kết nối. Các đường dẫn lơ lửng có thể hoạt động như ăng-ten. Chúng gây ra bức xạ dư thừa và có thể thu nhận nhiễu. Hãy tránh điều này.

Quy tắc kiểm tra vòng kín

Tránh để tín hiệu tạo thành vòng lặp qua các lớp khác nhau. Trong bảng mạch đa lớp, các vòng lặp gây ra nhiễu điện từ. Hãy chú ý đến điều này và điều chỉnh đường dẫn tín hiệu.

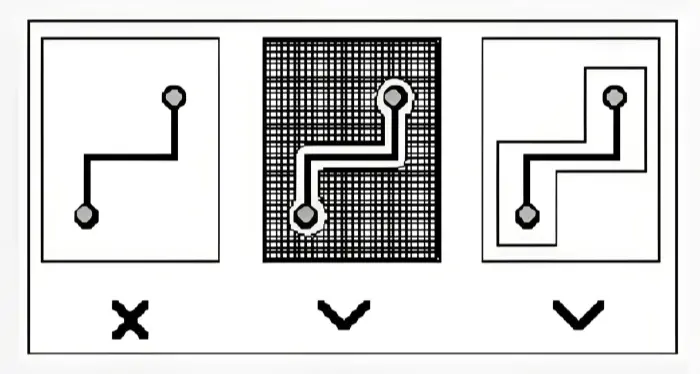

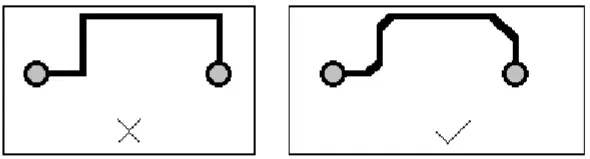

Quy tắc vát cạnh

Tránh sử dụng các góc nhọn hoặc góc vuông tại các góc của đường mạch. Các góc nhọn có thể gây ra bức xạ không mong muốn. Chúng cũng có thể gây khó khăn trong quá trình sản xuất. Nên sử dụng các đường cong nhẹ nhàng hoặc góc 45 độ.

Quy tắc tách biệt các thành phần

Thêm tụ điện cách ly khi cần thiết. Tụ điện cách ly giúp lọc nhiễu trên đường dây nguồn. Đặt tụ điện cách ly gần chân cấp nguồn của thiết bị, sau bộ lọc nguồn.

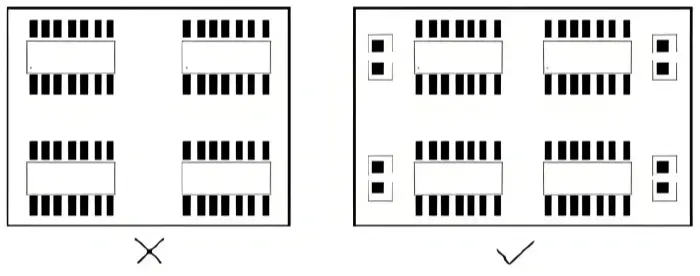

Tính toàn vẹn của các lớp nguồn và lớp đất

Ở những khu vực có nhiều lỗ via, không nên để các lỗ via cắt ngang qua mặt phẳng, khiến mặt phẳng bị chia thành các phần nhỏ hơn. Việc chia tách mặt phẳng sẽ làm tăng diện tích vòng lặp và gây ra các vấn đề về đường dẫn tín hiệu trở về. Khi thực hiện việc phân nhánh (fanout), hãy duy trì khoảng cách giữa các lỗ via sao cho vẫn có thể bố trí ít nhất một đường dẫn giữa các lỗ via.

Quy tắc chồng chéo mặt phẳng điện

Tránh để các lớp nguồn điện khác nhau chồng chéo lên nhau trong không gian. Điều này giúp giảm nhiễu giữa các nguồn điện, đặc biệt là khi các nguồn điện này có chênh lệch điện áp lớn. Nếu không thể tránh được sự chồng chéo, hãy cân nhắc thêm một lớp nối đất giữa chúng.

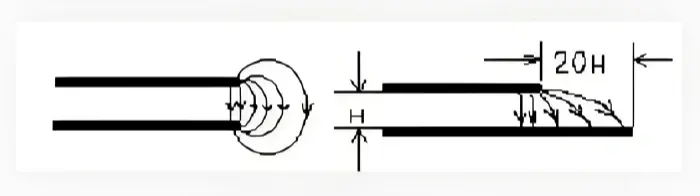

Quy tắc 20H được nhắc lại

Hãy lưu ý đến hiệu ứng biên. Khoảng cách giữa mặt phẳng nguồn và mặt phẳng đất ảnh hưởng đến sự bức xạ ở biên. Hãy lùi mặt phẳng nguồn vào trong để giữ trường điện từ nằm bên trong mặt phẳng đất. Việc lùi vào 20H sẽ giới hạn khoảng 70% của trường điện từ. Việc lùi vào 100H sẽ giới hạn khoảng 98% của trường điện từ.

Các quy tắc định tuyến và kiểm tra chi tiết hơn

Kiểm soát đường truyền ngược

Luôn lên kế hoạch cho đường dẫn trở về của tín hiệu. Tín hiệu phải có đường dẫn trở về có trở kháng thấp. Giữ cho đường dẫn trở về đất càng ngắn càng tốt.

Lập kế hoạch phân nhánh và via

Đối với các linh kiện BGA có mật độ cao hoặc khoảng cách chân cắm nhỏ, cần lên kế hoạch phân phối tín hiệu từ sớm. Giữ khoảng cách giữa các lỗ via sao cho vẫn có đủ không gian để đi dây tín hiệu. Đối với việc phân phối tín hiệu, nên sử dụng microvias hoặc blind vias nếu cần thiết trong các thiết kế tiên tiến.

Kiểm soát trở kháng

Đối với các đường dẫn đơn đầu hoặc cặp vi sai tốc độ cao, hãy điều chỉnh chiều rộng và khoảng cách giữa các đường dẫn sao cho phù hợp với trở kháng mục tiêu. Sử dụng cấu trúc lớp PCB và vật liệu điện môi để tính toán hình học của đường dẫn.

Định tuyến cặp vi sai

Định tuyến các cặp đường dẫn có độ dài bằng nhau. Giữ khoảng cách ổn định. Tránh các đoạn đường dẫn ngắn. Đảm bảo các khúc cua được uốn cong mượt mà.

Điều chỉnh độ dài và độ trễ

Đối với các đường dẫn và giao diện yêu cầu đồng bộ thời gian, hãy đảm bảo độ dài đường dẫn tương ứng. Sử dụng các đường dẫn uốn lượn để điều chỉnh độ dài. Đảm bảo các mẫu đường dẫn uốn lượn phải mượt mà và có chiều cao ngắn.

Miếng dán giảm đau do nhiệt và miếng dán giữ nhiệt

Khi gắn các miếng đệm lên các tấm đồng lớn, hãy sử dụng biện pháp giảm nhiệt. Hãy kết nối miếng đệm với mặt phẳng bằng các đường nối hình nan hoa. Điều này sẽ giúp quá trình hàn diễn ra thuận lợi hơn.

Lớp phủ chống hàn và lớp phủ bột hàn

Kiểm tra các lỗ trên lớp phủ chống hàn. Căn chỉnh khuôn in keo hàn cho các linh kiện SMD. Đảm bảo các điểm hàn nhỏ có diện tích keo hàn chính xác.

Thiết kế để kiểm tra và lắp ráp

Giữ lại các điểm kiểm tra và dấu hiệu lắp ráp. Giữ khoảng trống cho đầu dò. Sắp xếp linh kiện sao cho thuận tiện cho việc hàn và kiểm tra.

Danh sách kiểm tra định tuyến cuối cùng (danh sách tóm tắt)

• Kiểm tra xem tất cả các đường mạch đã được kết nối chưa.• Chạy các kiểm tra DRC và ERC.• Kiểm tra độ rộng đường mạch và dòng điện.• Kiểm tra khoảng cách để đảm bảo không bị nhiễu chéo và điện áp.• Kiểm tra tụ điện cách ly và tụ điện chính.• Kiểm tra việc chia lớp và đường dẫn trở về.• Kiểm tra các vùng tản nhiệt và hình dạng chân hàn.• Kiểm tra khả năng lắp ráp và tiếp cận để kiểm tra.

Những lỗi thường gặp cần tránh

• Để lại các khe mặt phẳng nối đất dưới các tín hiệu quan trọng.• Đặt các đường dẫn tốc độ cao cạnh các đường dẫn nguồn có nhiễu.• Sử dụng nhiều góc 90 độ.• Không thêm các mạch tách nhiễu gần các chân IC.• Để các lỗ vias làm chia cắt mặt phẳng nối đất một cách bất hợp lý.• Không lập kế hoạch phân nhánh cho các chip có mật độ cao.

Lời kết

Việc bố trí đường mạch là một phần quan trọng trong thiết kế PCB. Một bản bố trí đường mạch tốt sẽ đảm bảo các kết nối chính xác, hiệu suất cao và hình thức thẩm mỹ. Hãy tuân thủ các quy tắc đơn giản sau: Giữ cho các vòng lặp có kích thước nhỏ. Kiểm soát hiện tượng nhiễu chéo và đường dẫn hồi lưu. Sử dụng các vùng lún mặt phẳng để kiểm soát cạnh. Áp dụng các biện pháp cách ly để giảm nhiễu nguồn. Sử dụng các vùng giảm nhiệt để hỗ trợ quá trình hàn. Sử dụng lưới bố trí hợp lý. Kiểm tra kỹ lưỡng bảng mạch sau khi hoàn thành việc bố trí.

Nếu tuân thủ các nguyên tắc cơ bản này, bạn sẽ giảm thiểu nhiễu điện từ (EMI), nâng cao chất lượng tín hiệu và giúp việc lắp ráp và bảo trì bảng mạch trở nên dễ dàng hơn. Việc bố trí đường dẫn cần được thực hiện cẩn thận. Hãy dành thời gian cho công tác lập kế hoạch và bố trí mạch. Một bản thiết kế mạch tốt sẽ mang lại lợi ích về mặt tiết kiệm thời gian trong quá trình kiểm tra và sửa chữa, cũng như góp phần nâng cao chất lượng sản phẩm cuối cùng.